Multiprocessing

# Contents

| 1 | Mul        | tiproces | sing                                      | 1  |

|---|------------|----------|-------------------------------------------|----|

|   | 1.1        | Pre-his  | story                                     | 1  |

|   | 1.2        | Key top  | pics                                      | 1  |

|   |            | 1.2.1    | Processor symmetry                        | 1  |

|   |            | 1.2.2    | Instruction and data streams              | 1  |

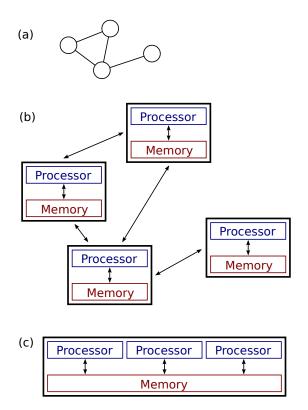

|   |            | 1.2.3    | Processor coupling                        | 2  |

|   |            | 1.2.4    | Multiprocessor Communication Architecture | 2  |

|   | 1.3        | Flynn's  | s taxonomy                                | 2  |

|   |            | 1.3.1    | SISD multiprocessing                      | 2  |

|   |            | 1.3.2    | SIMD multiprocessing                      | 2  |

|   |            | 1.3.3    | MISD multiprocessing                      | 3  |

|   |            | 1.3.4    | MIMD multiprocessing                      | 3  |

|   | 1.4        | See als  | 0                                         | 3  |

|   | 1.5        | Referen  | nces                                      | 3  |

| 2 | Com        |          | nultita shin s                            | 5  |

| 4 |            | -        | nultitasking                              | -  |

|   | 2.1<br>2.2 | -        | rogramming                                | 5  |

|   | 2.2        | _        | rative multitasking                       | 6  |

|   |            | -        | ptive multitasking                        | 6  |

|   | 2.4        |          | me                                        | 7  |

|   | 2.5        |          | nreading                                  | 7  |

|   | 2.6<br>2.7 |          | ry protection                             | 7  |

|   |            |          | ry swapping                               | 7  |

|   | 2.8<br>2.9 | -        | mming                                     | 7  |

|   |            |          | 0                                         | 8  |

|   | 2.10       | Referen  | nces                                      | 8  |

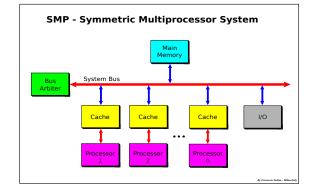

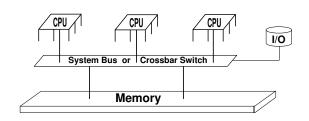

| 3 | Sym        | metric 1 | multiprocessing                           | 9  |

|   | 3.1        | Design   |                                           | 9  |

|   | 3.2        | History  | /                                         | 9  |

|   | 3.3        | Uses .   |                                           | 10 |

|   | 3.4        | Program  | mming                                     | 10 |

|   | 3.5        | Perform  | nance                                     | 10 |

|   | 3.6  | Systems                      | 10 |

|---|------|------------------------------|----|

|   |      | 3.6.1 Entry-level systems    | 10 |

|   |      | 3.6.2 Mid-level systems      | 11 |

|   | 3.7  | Alternatives                 | 11 |

|   | 3.8  | See also                     | 11 |

|   | 3.9  | References                   | 12 |

|   | 3.10 | External links               | 12 |

| 4 | Asyn | mmetric multiprocessing      | 13 |

|   | 4.1  | Background and history       | 13 |

|   | 4.2  | Burroughs B5000 and B5500    | 13 |

|   | 4.3  | CDC 6500 and 6700            | 14 |

|   | 4.4  | DECsystem-1055               | 14 |

|   | 4.5  | PDP-11/74                    | 14 |

|   | 4.6  | VAX-11/782                   | 14 |

|   | 4.7  | Univac 1108-II               | 14 |

|   | 4.8  | IBM System/370 model 168     | 14 |

|   | 4.9  | See also                     | 14 |

|   | 4.10 | Notes                        | 14 |

|   | 4.11 | References                   | 15 |

|   | 4.12 | External links               | 15 |

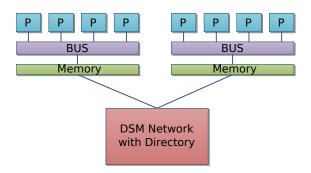

| 5 | Non- | -uniform memory access       | 16 |

|   | 5.1  | Basic concept                | 16 |

|   | 5.2  | Cache coherent NUMA (ccNUMA) | 17 |

|   | 5.3  | NUMA vs. cluster computing   | 17 |

|   | 5.4  | Software support             | 17 |

|   | 5.5  | See also                     | 17 |

|   | 5.6  | References                   | 18 |

|   | 5.7  | External links               | 18 |

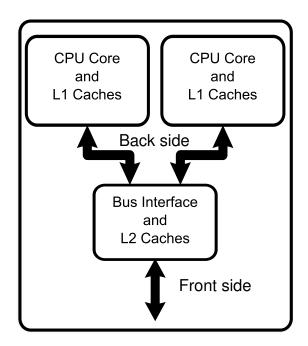

| 6 | Mult | ti-core processor            | 19 |

|   | 6.1  | Terminology                  | 20 |

|   | 6.2  | Development                  | 20 |

|   |      | 6.2.1 Commercial incentives  | 20 |

|   |      | 6.2.2 Technical factors      | 20 |

|   |      | 6.2.3 Advantages             | 21 |

|   |      | 6.2.4 Disadvantages          | 21 |

|   | 6.3  | Hardware                     | 21 |

|   |      | 6.3.1 Trends                 | 21 |

|   |      |                              |    |

|   |      | 6.3.2 Architecture           | 22 |

|   |          | 6.4.1 Licensing                     | 23        |

|---|----------|-------------------------------------|-----------|

|   | 6.5      | Embedded applications               | 23        |

|   | 6.6      | Hardware examples                   | 23        |

|   |          | 6.6.1 Commercial                    | 23        |

|   |          | 6.6.2 Free                          | 25        |

|   |          | 6.6.3 Academic                      | 25        |

|   | 6.7      | Benchmarks                          | 25        |

|   | 6.8      | Notes                               | 25        |

|   | 6.9      | See also                            | 26        |

|   | 6.10     | References                          | 26        |

|   | 6.11     | External links                      | 26        |

| _ | <b>.</b> |                                     | _         |

| 7 |          |                                     | 27        |

|   | 7.1      |                                     | 27        |

|   | 7.2      | Instruction set architecture        |           |

|   |          |                                     | 27        |

|   |          |                                     | 28        |

|   | 7.3      |                                     | 28        |

|   | 7.4      |                                     | 28        |

|   | 7.5      |                                     | 28        |

|   | 7.6      |                                     | 29        |

|   | 7.7      | 1                                   | 29        |

|   | 7.8      |                                     | 29        |

|   | 7.9      |                                     | 29        |

|   | 7.10     | References                          | 31        |

|   | 7.11     | External links                      | 31        |

| 8 | Intel    | Core                                | 32        |

|   | 8.1      | Overview                            | 32        |

|   | 8.2      | Enhanced Pentium M based            | 32        |

|   |          | 8.2.1 Core Duo                      | 32        |

|   |          | 8.2.2 Core Solo                     | 32        |

|   | 8.3      | 64-bit Core microarchitecture based | 33        |

|   |          | 8.3.1 Core 2 Solo                   | 33        |

|   |          | 8.3.2 Core 2 Duo                    | 33        |

|   |          | 8.3.3 Core 2 Quad                   | 33        |

|   |          | -                                   | 33        |

|   | 8.4      |                                     | 33        |

|   |          |                                     | 34        |

|   |          |                                     | 34        |

|   |          |                                     | , .<br>34 |

|   | 8.5      |                                     | 35        |

|   |          | • •                                 |           |

|    |                                                            | 8.5.1                                                    | Core i3                                                                                                                                                                                                    | 35                                                  |

|----|------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|    |                                                            | 8.5.2                                                    | Core i5                                                                                                                                                                                                    | 35                                                  |

|    |                                                            | 8.5.3                                                    | Core i7                                                                                                                                                                                                    | 35                                                  |

|    | 8.6                                                        | Ivy Bri                                                  | dge microarchitecture based                                                                                                                                                                                | 35                                                  |

|    |                                                            | 8.6.1                                                    | Core i3                                                                                                                                                                                                    | 35                                                  |

|    |                                                            | 8.6.2                                                    | Core i5                                                                                                                                                                                                    | 35                                                  |

|    |                                                            | 8.6.3                                                    | Core i7                                                                                                                                                                                                    | 35                                                  |

|    | 8.7                                                        | Haswel                                                   | l microarchitecture based                                                                                                                                                                                  | 35                                                  |

|    |                                                            | 8.7.1                                                    | Core i3                                                                                                                                                                                                    | 36                                                  |

|    |                                                            | 8.7.2                                                    | Core i5                                                                                                                                                                                                    | 36                                                  |

|    |                                                            | 8.7.3                                                    | Core i7                                                                                                                                                                                                    | 36                                                  |

|    | 8.8                                                        | Broadv                                                   | vell microarchitecture based                                                                                                                                                                               | 36                                                  |

|    |                                                            | 8.8.1                                                    | Core i3                                                                                                                                                                                                    | 36                                                  |

|    |                                                            | 8.8.2                                                    | Core i5                                                                                                                                                                                                    | 36                                                  |

|    |                                                            | 8.8.3                                                    | Core i7                                                                                                                                                                                                    | 36                                                  |

|    |                                                            | 8.8.4                                                    | Core M                                                                                                                                                                                                     | 36                                                  |

|    | 8.9                                                        | See als                                                  | o                                                                                                                                                                                                          | 36                                                  |

|    | 8.10                                                       | Referen                                                  | nces                                                                                                                                                                                                       | 36                                                  |

|    | 8.11                                                       | Externa                                                  | al links                                                                                                                                                                                                   | 37                                                  |

| 9  | List                                                       | of Intel                                                 | Core i5 microprocessors                                                                                                                                                                                    | 38                                                  |

| ,  | 9.1                                                        |                                                          | -                                                                                                                                                                                                          | 38                                                  |

|    | 9.1                                                        | 9.1.1                                                    | 1                                                                                                                                                                                                          | 38                                                  |

|    |                                                            | 9.1.1                                                    |                                                                                                                                                                                                            | 38                                                  |

|    |                                                            | 9.1.2                                                    | -                                                                                                                                                                                                          | 38                                                  |

|    |                                                            | 9.1.5<br>9.1.4                                           |                                                                                                                                                                                                            | 39                                                  |

|    |                                                            | 9.1.4                                                    |                                                                                                                                                                                                            | 39<br>39                                            |

|    | 9.2                                                        |                                                          |                                                                                                                                                                                                            | 39<br>39                                            |

|    | 9.2                                                        | 9.2.1                                                    | -                                                                                                                                                                                                          | 39<br>39                                            |

|    |                                                            | 9.2.1                                                    | -                                                                                                                                                                                                          | 39<br>40                                            |

|    |                                                            |                                                          |                                                                                                                                                                                                            | 40                                                  |

|    |                                                            | 0 2 2                                                    | Les Deides misses and its store (2nd segmention)                                                                                                                                                           | 10                                                  |

|    |                                                            | 9.2.3                                                    |                                                                                                                                                                                                            | 40                                                  |

|    |                                                            | 9.2.4                                                    | Haswell microarchitecture (4th generation)                                                                                                                                                                 | 40                                                  |

|    | 0.2                                                        | 9.2.4<br>9.2.5                                           | Haswell microarchitecture (4th generation)                                                                                                                                                                 | 40<br>41                                            |

|    | 9.3                                                        | 9.2.4<br>9.2.5<br>See als                                | Haswell microarchitecture (4th generation)    4      Broadwell microarchitecture (5th generation)    4      0    6                                                                                         | 40<br>41<br>41                                      |

|    | 9.4                                                        | 9.2.4<br>9.2.5<br>See als<br>Notes                       | Haswell microarchitecture (4th generation)    4      Broadwell microarchitecture (5th generation)    4      0    1      1    1      1    1      1    1      2    1                                         | 40<br>41<br>41<br>41                                |

|    | 9.4<br>9.5                                                 | 9.2.4<br>9.2.5<br>See als<br>Notes<br>Referen            | Haswell microarchitecture (4th generation)    4      Broadwell microarchitecture (5th generation)    4      o    1      nces    4                                                                          | 40<br>41<br>41<br>41<br>41                          |

|    | 9.4                                                        | 9.2.4<br>9.2.5<br>See als<br>Notes<br>Referen            | Haswell microarchitecture (4th generation)    4      Broadwell microarchitecture (5th generation)    4      o    4                                                                                         | 40<br>41<br>41<br>41                                |

| 10 | <ol> <li>9.4</li> <li>9.5</li> <li>9.6</li> </ol>          | 9.2.4<br>9.2.5<br>See als<br>Notes<br>Referen<br>Externa | Haswell microarchitecture (4th generation)       4         Broadwell microarchitecture (5th generation)       4         o       1         nces       4         al links       4                            | 40<br>41<br>41<br>41<br>41                          |

| 10 | <ul><li>9.4</li><li>9.5</li><li>9.6</li><li>Pent</li></ul> | 9.2.4<br>9.2.5<br>See als<br>Notes<br>Referen<br>Externa | Haswell microarchitecture (4th generation)       4         Broadwell microarchitecture (5th generation)       4         o       4         inces       4         al links       4         al-Core       4   | 40<br>41<br>41<br>41<br>41<br>41                    |

| 10 | <ul><li>9.4</li><li>9.5</li><li>9.6</li><li>Pent</li></ul> | 9.2.4<br>9.2.5<br>See als<br>Notes<br>Referen<br>Externa | Haswell microarchitecture (4th generation)       4         Broadwell microarchitecture (5th generation)       4         o       4         inces       4         al links       4         sor cores       4 | 40<br>41<br>41<br>41<br>41<br>41<br>41<br><b>42</b> |

|    | 10.1.3 Merom-2M                                                                                        | 43 |

|----|--------------------------------------------------------------------------------------------------------|----|

|    | 10.1.4 Wolfdale-3M                                                                                     | 43 |

|    | 10.1.5 Penryn-3M                                                                                       | 43 |

|    | 10.2 Rebranding                                                                                        | 43 |

|    | 10.3 Comparison to the Pentium D                                                                       | 43 |

|    | 10.4 See also                                                                                          | 43 |

|    | 10.5 References                                                                                        | 44 |

|    | 10.6 External links                                                                                    | 44 |

| 11 | Xeon                                                                                                   | 45 |

|    | 11.1 Overview                                                                                          | 45 |

|    | 11.2 P6-based Xeon                                                                                     | 45 |

|    | 11.2.1 Pentium II Xeon                                                                                 | 45 |

|    | 11.2.2 Pentium III Xeon                                                                                | 45 |

|    | 11.3 Netburst-based Xeon                                                                               | 46 |

|    | 11.3.1 Xeon (DP) & Xeon MP (32-bit)                                                                    | 46 |

|    | 11.3.2 "Gallatin"                                                                                      | 46 |

|    | 11.3.3 Xeon (DP) & Xeon MP (64-bit)                                                                    | 46 |

|    | 11.3.4 Dual-Core Xeon                                                                                  | 47 |

|    | 11.4 Pentium M (Yonah) based Xeon                                                                      | 47 |

|    | 11.4.1 LV (ULV), "Sossaman"                                                                            | 47 |

|    | 11.5 Core-based Xeon                                                                                   | 48 |

|    | 11.5.1 Dual-Core                                                                                       | 48 |

|    | 11.5.2 Quad-Core and Multi-Core Xeon                                                                   | 48 |

|    | 11.6 Nehalem-based Xeon                                                                                | 50 |

|    | 11.6.1 3400-series "Lynnfield"                                                                         | 50 |

|    | 11.6.2 3400-series "Clarkdale"                                                                         | 50 |

|    | 11.6.3 3500-series "Bloomfield"                                                                        | 50 |

|    | 11.6.4 <span gainestown""="" id="5500-series ">5500-series "Gainestown"</span>                         | 51 |

|    | 11.6.5 <span forest""="" id="C3500/C5500-Series " jasper="">C3500/C5500-series "Jasper Forest"</span>  | 51 |

|    | 11.6.6 3600/5600-series "Gulftown" & "Westmere-EP"                                                     | 51 |

|    | 11.6.7 6500/7500-series "Beckton"                                                                      | 51 |

|    | 11.6.8 E7-x8xx-series "Westmere-EX"                                                                    | 51 |

|    | 11.7 Sandy Bridge– and Ivy Bridge–based Xeon                                                           | 52 |

|    | 11.7.1 E3-12xx-series "Sandy Bridge"                                                                   | 52 |

|    | 11.7.2 E3-12xx v2-series "Ivy Bridge"                                                                  | 52 |

|    | 11.7.3 E5-14xx/24xx series "Sandy Bridge-EN" and E5-16xx/26xx/46xx-series "Sandy Bridge-EP"            | 52 |

|    | 11.7.4 E5-14xx v2/24xx v2 series "Ivy Bridge-EN" and E5-16xx v2/26xx v2/46xx v2 series "Ivy Bridge-EP" | 52 |

|    | 11.7.5 E7-28xx v2/48xx v2/88xx v2 series "Ivy Bridge-EX"                                               | 52 |

|    | 11.8 Haswell-based Xeon                                                                                | 52 |

|    | 11.8.1 E3-12xx v3-series "Haswell"                                                                     | 53 |

| 12.1       Introduction         12.1.1       Architecture         12.2       Parallel and distributed computing         12.3       History         12.4       Applications         12.5       Examples         12.6.1       Models         12.6.2       An example         12.6.3       Complexity measures         12.6.4       Other problems         12.6.5       Properties of distributed systems         12.6.6       Other problems         12.6.7       Poordinator election         12.7.1       Bully algorithm         12.7.2       Chang and Roberts algorithm         12.7.3       See also         12.10Notes       12.11References         12.11References       12.12Further reading         12.13External links       13.1         13.1       Definitions         13.2       Overview         13.3       SOA framework         13.4       Design concept         13.5.1       Service architecture         13.5.2       Service composition architecture         13.5.3       Service inventory architecture         13.5.4       Service oriented enethitecture         13.5.5 <t< th=""><th>11.8.2 E5-16xx/26xx v3-series "Haswell-EP"</th><th> 53</th></t<>                                                        | 11.8.2 E5-16xx/26xx v3-series "Haswell-EP" | 53 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----|

| 11.11References         11.12External links         12 Distributed computing         12.1 Introduction         12.1.1 Architecture         12.2 Parallel and distributed computing         12.3 History         12.4 Applications         12.5 Examples         12.6 Theoretical foundations         12.6.1 Models         12.6.2 An example         12.6.3 Complexity measures         12.6.4 Other problems         12.6.5 Properties of distributed systems         12.7.1 Bully algorithm         12.7.2 Chang and Roberts algorithm         12.7.3 Extinctures         12.8 Architectures         12.10Notes         12.11References         12.12Further reading         12.13External links         13 Definitions         13.2 Overview         13.3 SOA framework         13.4 Design concept         13.5.1 Service architecture         13.5.1 Service inventory architecture         13.5.3 Service origentied enterprise architecture         13.5.4 Service inventory architecture         13.5.3 Service inventory architecture         13.5.4 Service protocols                                                                                                                                                        | 11.9 Supercomputers                        | 53 |

| 11.12External links         12 Distributed computing         12.1 Introduction         12.1.1 Architecture         12.2 Parallel and distributed computing         12.3 History         12.4 Applications         12.5 Examples         12.6.1 Models         12.6.2 An example         12.6.3 Complexity measures         12.6.4 Other problems         12.6.5 Properties of distributed systems         12.6.7 Coordinator election         12.7.1 Bully algorithm         12.7.2 Chang and Roberts algorithm         12.7.3 Chang and Roberts algorithm         12.7.4 Charther reading         12.1.7 Covertimed architecture         13.1 Service-oriented architecture         13.1 Definitions         13.2 Overview         13.3 SOA framework         13.4 Design concept         13.5.1 Service architecture         13.5.2 Service oriention architecture         13.5.4 Service architecture         13.5.4 Service architecture         13.5.4 Service architecture         13.5.4 Service architecture         13.5.5 Service inventory architecture         13.5.4 Service architecture         13.5.4 Service oriention architecture         13.5.4 Service oriention architecture <td>11.10See also</td> <td> 53</td> | 11.10See also                              | 53 |

| 12 Distributed computing         12.1.1 Architecture         12.2 Parallel and distributed computing         12.3 History         12.4 Applications         12.5 Examples         12.6 Theoretical foundations         12.6.1 Models         12.6.2 An example         12.6.3 Complexity measures         12.6.4 Other problems         12.6.5 Properties of distributed systems         12.7.1 Bully algorithm         12.7.2 Charg and Roberts algorithm         12.7.3 Charg and Roberts algorithm         12.8 Architectures         12.9 See also         12.11References         12.13External links         13 Service-oriented architecture         13.3 SOA framework         13.4 Design concept         13.5.1 Service architecture         13.5.2 Service oriented architecture         13.5.3 Service oriented enchitecture         13.5.4 Service oriented enchitecture         13.5.5 Service inventory architecture         13.5.1 Service architecture         13.5.4 Service oriented enchitecture         13.5.4 Service oriented enchitecture         13.5.5 Service inventory architecture         13.5.7 Service inventory architecture         13.5.8 Service oriented enchitecture      <                      | 11.11References                            | 54 |

| 12.1       Introduction         12.1.1       Architecture         12.2       Parallel and distributed computing         12.3       History         12.4       Applications         12.5       Examples         12.6       Theoretical foundations         12.6.1       Models         12.6.2       An example         12.6.3       Complexity measures         12.6.4       Other problems         12.6.5       Properties of distributed systems         12.7.1       Bully algorithm         12.7.2       Chang and Roberts algorithm         12.7.3       Chang and Roberts algorithm         12.7.4       See also         12.11References       12.11References         12.11References       12.12Further reading         12.13External links       13         13       Service-oriented architecture         13.1       Definitions         13.2       Overview         13.3       SOA framework         13.4       Design concept         13.5.1       Service architecture         13.5.2       Service composition architecture         13.5.3       Service inventory architecture         13.5.4 </th <td>11.12External links</td> <td> 54</td>                                                                            | 11.12External links                        | 54 |

| 12.1       Introduction         12.1.1       Architecture         12.2       Parallel and distributed computing         12.3       History         12.4       Applications         12.5       Examples         12.6       Theoretical foundations         12.6.1       Models         12.6.2       An example         12.6.3       Complexity measures         12.6.4       Other problems         12.6.5       Properties of distributed systems         12.7.1       Bully algorithm         12.7.2       Chang and Roberts algorithm         12.7.3       Chang and Roberts algorithm         12.7.4       See also         12.11References       12.11References         12.11References       12.12Further reading         12.13External links       13         13       Service-oriented architecture         13.1       Definitions         13.2       Overview         13.3       SOA framework         13.4       Design concept         13.5.1       Service architecture         13.5.2       Service composition architecture         13.5.3       Service inventory architecture         13.5.4 </th <th>12 Distributed computing</th> <th>55</th>                                                                        | 12 Distributed computing                   | 55 |

| 12.1 Architecture         12.2 Parallel and distributed computing         12.3 History         12.4 Applications         12.5 Examples         12.6 Theoretical foundations         12.6.1 Models         12.6.2 An example         12.6.3 Complexity measures         12.6.4 Other problems         12.6.5 Properties of distributed systems         12.7.1 Bully algorithm         12.7.2 Chang and Roberts algorithm         12.8 Architectures         12.9 See also         12.10Notes         12.11References         12.12Further reading         12.13External links         13 Service-oriented architecture         13.5 Principles         13.5.1 Service architecture         13.5.1 Service architecture         13.5.1 Service inventory architecture         13.5.1 Service intertory architecture         13.5.1 Service interetory architecture                                     |                                            |    |

| 12.2       Parallel and distributed computing         12.3       History         12.4       Applications         12.5       Examples         12.6       Theoretical foundations         12.6.1       Models         12.6.2       An example         12.6.3       Complexity measures         12.6.4       Other problems         12.6.5       Properties of distributed systems         12.6.6       Other problems         12.6.7       Coordinator election         12.7.1       Bully algorithm         12.7.2       Chang and Roberts algorithm         12.7.3       See also         12.10Notes       12.11References         12.11References       12.12Further reading         12.13External links       13.1         13       Service-oriented architecture         13.1       Definitions         13.2       Overview         13.3       SOA framework         13.4       Design concept         13.5       Principles         13.5.1       <                                                                                                                              |                                            |    |

| 12.3 History         12.4 Applications         12.5 Examples         12.6 Theoretical foundations         12.6.1 Models         12.6.2 An example         12.6.3 Complexity measures         12.6.4 Other problems         12.6.5 Properties of distributed systems         12.6.6 Properties of distributed systems         12.7.1 Bully algorithm         12.7.2 Chang and Roberts algorithm         12.8 Architectures         12.9 See also         12.10Notes         12.11References         12.12Further reading         12.13External links         13 Service-oriented architecture         13.1 Definitions         13.2 Overview         13.3 SOA framework         13.4 Design concept         13.5 Principles         13.5.1 Service architecture         13.5.2 Service composition architecture         13.5.3 Service inventory architecture         13.5.4 Service inventory architecture         13.5.4 Service inventory architecture <t< th=""><th></th><th></th></t<>                      |                                            |    |

| 12.4 Applications         12.5 Examples         12.6 Theoretical foundations         12.6.1 Models         12.6.2 An example         12.6.3 Complexity measures         12.6.4 Other problems         12.6.5 Properties of distributed systems         12.7 Coordinator election         12.7.1 Bully algorithm         12.7.2 Chang and Roberts algorithm         12.7.2 Chang and Roberts algorithm         12.7.3 Chang and Roberts algorithm         12.7.4 Sectores         12.9 See also         12.10Notes         12.11References         12.12Further reading         12.13External links         13.5 Overview         13.5 Overview         13.5 Principles         13.5.1 Service architecture         13.5.2 Service architecture         13.5.3 Service inventory architecture         13.5.4 Service-oriented enterprise architecture         13.5.4 Service approach         13.5.7 Web service approach                                                                                                                                                                                                                                                                                                               |                                            |    |

| 12.5 Examples         12.6 Theoretical foundations         12.6.1 Models         12.6.2 An example         12.6.3 Complexity measures         12.6.4 Other problems         12.6.5 Properties of distributed systems         12.7 Coordinator election         12.7.1 Bully algorithm         12.7.2 Chang and Roberts algorithm         12.7.3 Coordinator election         12.7.4 Condinator election         12.7.5 Condinator election         12.7.6 Condinator election         12.7.7 Condinator election         12.7.7 Condinator election         12.7.1 Bully algorithm         12.7.2 Chang and Roberts algorithm         12.7.2 Chang and Roberts algorithm         12.7.8 ealso         12.10 Notes         12.11 References         12.12 Further reading         12.12 Further reading         12.13 External links         13 Service-oriented architecture         13.1 Definitions         13.2 Overview         13.3 SOA framework         13.4 Design concept         13.5 Principles         13.5.1 Service architecture         13.5.2 Service composition architecture         13.5.3 Service inventory architecture         13.5.4 Service-oriente                                                            |                                            |    |

| 12.6 Theoretical foundations         12.6.1 Models         12.6.2 An example         12.6.3 Complexity measures         12.6.4 Other problems         12.6.5 Properties of distributed systems         12.7 Coordinator election         12.7.1 Bully algorithm         12.7.2 Chang and Roberts algorithm         12.8 Architectures         12.9 See also         12.10Notes         12.12Further reading         12.13External links         13 Service-oriented architecture         13.1 Definitions         13.2 Overview         13.3 SOA framework         13.4 Design concept         13.5.1 Service architecture         13.5.2 Service oriented anchitecture         13.5.3 Service inventory architecture         13.5.4 Service-oriented enterprise architecture         13.7 Web service protocols                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |    |

| 12.6.1       Models         12.6.2       An example         12.6.3       Complexity measures         12.6.4       Other problems         12.6.5       Properties of distributed systems         12.7       Coordinator election         12.7.1       Bully algorithm         12.7.2       Chang and Roberts algorithm         12.7.2       Chang and Roberts algorithm         12.7.3       See also         12.9       See also         12.10Notes       12.10Notes         12.11References       12.12Further reading         12.12Further reading       12.13External links         13       Service-oriented architecture         13.1       Definitions         13.2       Overview         13.3       SOA framework         13.4       Design concept         13.5.1       Service architecture         13.5.2       Service composition architecture         13.5.3       Service oriented enterprise architecture         13.5.4       Service-oriented enterprise architecture         13.6       Web service approach         13.7       Web service protocols                                                                                                                                                               | -                                          |    |

| 12.6.2 An example         12.6.3 Complexity measures         12.6.4 Other problems         12.6.5 Properties of distributed systems         12.6.5 Properties of distributed systems         12.6.7 Coordinator election         12.7.1 Bully algorithm         12.7.2 Chang and Roberts algorithm         12.7.9 See also         12.10 Notes         12.11 References         12.12 Further reading         12.13 External links         13 Service-oriented architecture         13.1 Definitions         13.2 Overview         13.3 SOA framework         13.4 Design concept         13.5.1 Service architecture         13.5.2 Service composition architecture         13.5.3 Service inventory architecture         13.5.4 Service-oriented enterprise architecture         13.6 Web services approach                                                                                                                                                                                                                                                                                                                                                                                                                         |                                            |    |

| 12.6.3       Complexity measures         12.6.4       Other problems         12.6.5       Properties of distributed systems         12.7.1       Bully algorithm         12.7.2       Chang and Roberts algorithm         12.0       Notes         12.10       Notes         12.11References       12.12         12.12Further reading       12.12         12.13External links       13.1         13.1       Definitions         13.2       Overview                                                                      |                                            |    |

| 12.6.4       Other problems         12.6.5       Properties of distributed systems         12.7       Coordinator election         12.7.1       Bully algorithm         12.7.2       Chang and Roberts algorithm         12.7.2       Chang and Roberts algorithm         12.7.2       Chang and Roberts algorithm         12.7.4       Chang and Roberts algorithm         12.7.5       Chang and Roberts algorithm         12.7.6       See also         12.7.7       Chang and Roberts algorithm         12.7.2       See also         12.10       Notes         12.10       Notes         12.10       Notes         12.11References       12.12         12.12       Further reading         12.12       Further reading         13.1       Definitions         13.2       Overview         13.3       SOA framework     <                                                                                                    | -                                          |    |

| 12.6.5       Properties of distributed systems         12.7       Coordinator election         12.7.1       Bully algorithm         12.7.2       Chang and Roberts algorithm         12.7.2       Chang and Roberts algorithm         12.7.3       State and Roberts algorithm         12.7.4       Chang and Roberts algorithm         12.7.5       Chang and Roberts algorithm         12.7.6       See also         12.7.7       Chang and Roberts algorithm         12.7.2       Chang and Roberts algorithm         12.7.2       Chang and Roberts algorithm         12.7.2       See also         12.10       See also         12.11       References         12.12       Further reading         12.12       Further reading         12.13       External links         13       Service-oriented architecture         13.1       Definitions         13.2       Overview         13.3       SOA framework         13.4       Design concept         13.5.1       Service architecture         13.5.2       Service composition architecture         13.5.3       Service inventory architecture         13.5.4       Service-ori                                                                                               |                                            |    |

| <ul> <li>12.7 Coordinator election .</li> <li>12.7.1 Bully algorithm .</li> <li>12.7.2 Chang and Roberts algorithm .</li> <li>12.8 Architectures .</li> <li>12.9 See also .</li> <li>12.10Notes .</li> <li>12.11References .</li> <li>12.12Further reading .</li> <li>12.13External links .</li> <li>13 Service-oriented architecture .</li> <li>13.1 Definitions .</li> <li>13.2 Overview .</li> <li>13.3 SOA framework .</li> <li>13.4 Design concept .</li> <li>13.5.1 Service architecture .</li> <li>13.5.2 Service composition architecture .</li> <li>13.5.3 Service inventory architecture .</li> <li>13.5.4 Service-oriented enterprise architecture .</li> <li>13.6 Web services approach .</li> <li>13.7 Web service protocols .</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                          |    |

| 12.7.1       Bully algorithm         12.7.2       Chang and Roberts algorithm         12.8       Architectures         12.9       See also         12.10Notes       12.10Notes         12.11References       12.11References         12.12Further reading       12.12Further reading         12.13External links       12         13 Service-oriented architecture       13.1         13.1       Definitions         13.2       Overview         13.3       SOA framework         13.4       Design concept         13.5       Principles         13.5.1       Service architecture         13.5.2       Service composition architecture         13.5.3       Service inventory architecture         13.5.4       Service-oriented enterprise architecture         13.6       Web services approach         13.7       Web service protocols                                                                                                                                                                                                                                                                                                                                                                                          |                                            |    |

| 12.7.2 Chang and Roberts algorithm         12.8 Architectures         12.9 See also         12.10Notes         12.11References         12.12Further reading         12.13External links         13 Service-oriented architecture         13.1 Definitions         13.2 Overview         13.3 SOA framework         13.4 Design concept         13.5 Principles         13.5.1 Service architecture         13.5.2 Service composition architecture         13.5.3 Service inventory architecture         13.5.4 Service-oriented enterprise architecture         13.5.7 Web services approach         13.7 Web service protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |    |

| 12.8 Architectures         12.9 See also         12.10Notes         12.11References         12.12Further reading         12.13External links         13 Service-oriented architecture         13.1 Definitions         13.2 Overview         13.3 SOA framework         13.4 Design concept         13.5 Principles         13.5.1 Service architecture         13.5.2 Service composition architecture         13.5.4 Service-oriented enterprise architecture         13.6 Web services approach         13.7 Web service protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                            |    |

| 12.10Notes         12.11References         12.12Further reading         12.13External links         13 Service-oriented architecture         13.1 Definitions         13.2 Overview         13.3 SOA framework         13.4 Design concept         13.5 Principles         13.5.1 Service architecture         13.5.2 Service composition architecture         13.5.3 Service inventory architecture         13.5.4 Service-oriented enterprise architecture         13.6 Web services approach         13.7 Web service protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                            |    |

| 12.11References         12.12Further reading         12.13External links         13 Service-oriented architecture         13.1 Definitions         13.2 Overview         13.3 SOA framework         13.4 Design concept         13.5 Principles         13.5.1 Service architecture         13.5.2 Service composition architecture         13.5.3 Service inventory architecture         13.5.4 Service-oriented enterprise architecture         13.6 Web services approach         13.7 Web service protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12.9 See also                              | 60 |

| 12.11References         12.12Further reading         12.13External links         13 Service-oriented architecture         13.1 Definitions         13.2 Overview         13.3 SOA framework         13.4 Design concept         13.5 Principles         13.5.1 Service architecture         13.5.2 Service composition architecture         13.5.3 Service inventory architecture         13.5.4 Service-oriented enterprise architecture         13.6 Web services approach         13.7 Web service protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12.10Notes                                 | 61 |

| 12.13External links         13 Service-oriented architecture         13.1 Definitions         13.2 Overview         13.3 SOA framework         13.4 Design concept         13.5 Principles         13.5.1 Service architecture         13.5.2 Service composition architecture         13.5.3 Service inventory architecture         13.5.4 Service-oriented enterprise architecture         13.6 Web services approach         13.7 Web service protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                            |    |

| 13 Service-oriented architecture         13.1 Definitions         13.2 Overview         13.3 SOA framework         13.4 Design concept         13.5 Principles         13.5.1 Service architecture         13.5.2 Service composition architecture         13.5.3 Service inventory architecture         13.5.4 Service-oriented enterprise architecture         13.6 Web services approach         13.7 Web service protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12.12Further reading                       | 62 |

| <ul> <li>13.1 Definitions</li> <li>13.2 Overview</li> <li>13.3 SOA framework</li> <li>13.4 Design concept</li> <li>13.5 Principles</li> <li>13.5.1 Service architecture</li> <li>13.5.2 Service composition architecture</li> <li>13.5.3 Service inventory architecture</li> <li>13.5.4 Service-oriented enterprise architecture</li> <li>13.6 Web services approach</li> <li>13.7 Web service protocols</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                          |    |

| <ul> <li>13.1 Definitions</li> <li>13.2 Overview</li> <li>13.3 SOA framework</li> <li>13.4 Design concept</li> <li>13.5 Principles</li> <li>13.5.1 Service architecture</li> <li>13.5.2 Service composition architecture</li> <li>13.5.3 Service inventory architecture</li> <li>13.5.4 Service-oriented enterprise architecture</li> <li>13.6 Web services approach</li> <li>13.7 Web service protocols</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            |    |

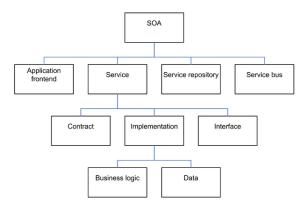

| <ul> <li>13.2 Overview</li> <li>13.3 SOA framework</li> <li>13.4 Design concept</li> <li>13.5 Principles</li> <li>13.5.1 Service architecture</li> <li>13.5.2 Service composition architecture</li> <li>13.5.3 Service inventory architecture</li> <li>13.5.4 Service-oriented enterprise architecture</li> <li>13.6 Web services approach</li> <li>13.7 Web service protocols</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                            | 64 |

| <ul> <li>13.3 SOA framework</li> <li>13.4 Design concept</li> <li>13.5 Principles</li> <li>13.5.1 Service architecture</li> <li>13.5.2 Service composition architecture</li> <li>13.5.3 Service inventory architecture</li> <li>13.5.4 Service-oriented enterprise architecture</li> <li>13.6 Web services approach</li> <li>13.7 Web service protocols</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                            |    |

| <ul> <li>13.4 Design concept</li> <li>13.5 Principles</li> <li>13.5.1 Service architecture</li> <li>13.5.2 Service composition architecture</li> <li>13.5.3 Service inventory architecture</li> <li>13.5.4 Service-oriented enterprise architecture</li> <li>13.6 Web services approach</li> <li>13.7 Web service protocols</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                            |    |

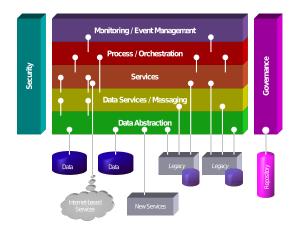

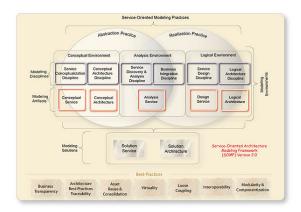

| 13.5 Principles         13.5.1 Service architecture         13.5.2 Service composition architecture         13.5.3 Service inventory architecture         13.5.4 Service-oriented enterprise architecture         13.6 Web services approach         13.7 Web service protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                            |    |

| 13.5.1       Service architecture         13.5.2       Service composition architecture         13.5.3       Service inventory architecture         13.5.4       Service-oriented enterprise architecture         13.6       Web services approach         13.7       Web service protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                            |    |

| <ul> <li>13.5.2 Service composition architecture</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                                          |    |

| 13.5.3 Service inventory architecture         13.5.4 Service-oriented enterprise architecture         13.6 Web services approach         13.7 Web service protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            |    |

| 13.5.4 Service-oriented enterprise architecture         13.6 Web services approach         13.7 Web service protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                            |    |

| 13.6 Web services approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                            |    |

| 13.7 Web service protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                            |    |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                            |    |

| 13.8 Other SOA concepts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |    |