Anbieter zum Thema

Ein Beispiel: Breite einer Leiterbahn oder Powerfläche für BGA

Die Ausgangslage: 10-Lagen Multilayer (½ oz Kupferfolie) mit impedanzrelevantem Aufbau (mehrere Versorgungsebenen) und 100 μm Leiterbreite/Abstand. Aufgrund der „Flutung“ auf den Versorgungsspannungen entstehen zwischen den Durchkontaktierungen Leitungskanäle, die typischerweise in der Breite einer einzelnen Leiterbahn entsprechen. Mit dem Ätzfaktor 1 (Worst-Case) reduziert sich die Leiterbreite von 100 μm auf 83 μm Breite. Prozentual gesehen bedeutet dies eine Reduzierung um 17 % auf 83 %.

Eine vorherige Verbreiterung der Leiterbahnen innerhalb der Datenaufbereitung beim Leiterplattenhersteller verhindert diesen Effekt nicht. Die Leiterbreite läge dann näher am nominellen Wert. Ist der Zuschlag bekannt, könnte er mit einbezogen werden.

Sind viele innenliegende BGA-Pins (z.B. GND 5 x 5-Pin-Raster) flächig anzuschließen, vervielfacht sich dieser Effekt. So könnten hier etwa nur Pinzahl n-1 (= 4) Leitungskanäle verwendet werden. Für die Worst-Case-Betrachtung würde sich die Breite nicht mehr als Fläche, sondern aus nominellen Leiterzügen á 4 x 100 μm = 400 μm, auf nun nutzbare 4 x 83 μm = 332 μm reduzieren. Ein weiterer Skaleneffekt ergäbe sich bei einem Multilayer-Aufbau, bei dem die Spannungsflächen über mehrere Lagen verteilt sind.

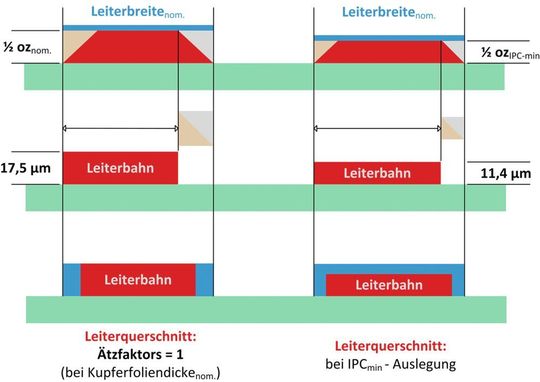

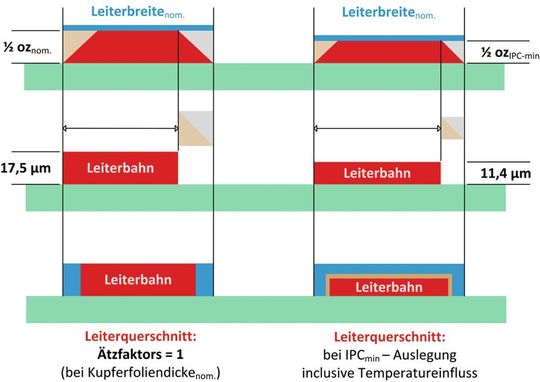

Die im ersten Teil erkannte Schichtdickenreduzierung bezogen sich auf 1 oz Schichtdicke der Kupferfolie (35 μm). In Multilayer-Aufbauten (ML) werden typischerweise für Innenlagen ½ oz Kupferfolien (17 μm) verwendet. Analog zu der vorangegangenen Betrachtung ergibt sich eine Kupferschicht von mindestens 11,4 µm (laut IPC-4562: 17,1 µm – 10 %) und - 4 µm Prozessverlust. Bezogen auf 17,5 μm sind das noch 65 % der nominellen Schichtdicke (Abbildung 2).

Im zweiten Teil wurde auf die durch die Ätzprozesse entstandene reduzierte und geometrisch geänderte Leiterbreite eingegangen. Durch die Parallelschaltung mehrerer Leiterbahnen wird versucht, die Leiterbreite (Querschnitt) effektiv zu erhöhen. Der Ätzfaktor kann die Leiterbreite bei parallel geschalteten Leitungen auf 83 % reduzieren. Mit beiden Vektoren ist es möglich, den Leiterquerschnitt zu berechnen: Nominell errechnet sich für den angenommenen Multilayer mit ½ oz Innenlagen (zum Beispiel drei davon als GND-Lagen) für 1,2 mm Gesamtbreite (12 Leiterzügen à 100 μm) ein Querschnitt von 0,021 mm2. Das Worst-Case-Szenario (12 Leiterzüge à 83 μm) mit erlaubter Mindestkupferschichtdicke von 11,4 μm ergäbe dagegen nur 0,0113 mm2. Im Ergebnis ist das nur noch etwas über 54 % des angenommenen Querschnittes!

Temperatureigenschaften von Kupfer

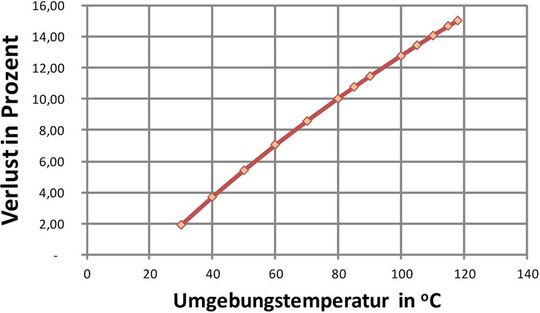

Der Werkstoff Kupfer besitzt wie alle Materialien temperaturabhängige Eigenschaften. Für unsere Betrachtung relevant ist der Temperaturkoeffizient (bei 20°C) von 0,00393 K. In der Praxis erhöht sich der Eigenwiderstand der Leiterbahn bei steigender Umgebungstemperatur. Vereinfacht beschrieben steigt der Eigenwiderstand der Leiterbahn bei Umgebung von 50°C um 5 %, 80°C um 10 % und bei 118°C um 15 %.

In der Fortführung des bisher skizzierten Beispiels ist der Bauraum der Leiterplatte um den μController aus thermischer Sicht ein HotSpot. Das heißt: Während des Betriebs wird eine Temperatur von 80°C angenommen, die auch auf die Leiterplatte eingeprägt wird. Zusammen mit den bisherigen Annahmen verknüpft, könnte die Worst-Case- Betrachtung wie folgt aussehen:

Um die gleiche Menge Strom über den nominellen Leiterquerschnitt von 0,021 mm2 verlustfrei zu transportieren müsste dieser bei 80°C um 10 % größer sein, als bisher ausgerechnet: Das sind: 0,0231 mm2.

In der Praxis ergäbe sich jedoch folgendes Szenario: Der durch die Fertigung realisierte und innerhalb der Fertigungstoleranzen liegende Querschnitt von 0,0113 mm2 würde sich entsprechend einem 0,0101 mm2 Leiterquerschnitt verhalten. Verglichen mit dem Querschnitt nominell werden nur noch weniger als 50 % erreicht (Abbildung 4).

Aus verschiedenen Gründen wie Produktentwicklungsstrategien oder Schaltungsabsicherungen muss also das sogenannte Worst-Case-Szenario betrachtet und bewertet werden. Zudem ist es wichtig, Strategien zu entwickeln, um den genannten Effekten entgegenzuwirken.

* Michael Schleicher ist PCB-Designer bei SEMIKRON

(ID:43712421)

:quality(80)/p7i.vogel.de/wcms/08/cb/08cb1b39d0e5c58591bc70e8b63a0220/0118078425.jpeg)

:quality(80)/p7i.vogel.de/wcms/8f/e8/8fe846e9bc5577c77430aee8a0a68599/0118091177.jpeg)

:quality(80)/p7i.vogel.de/wcms/de/89/de8956f8a3c454ac651a8ffa3303c89f/0117868030.jpeg)

:quality(80)/p7i.vogel.de/wcms/d6/10/d6101a2aac8c7d2cab2ff31546979254/0118103063.jpeg)

:quality(80)/p7i.vogel.de/wcms/29/c2/29c2b968dc07be08e6062d8e6d8c387b/0118061450.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/0f/0d0f07610ae64127bd49e5512e847f00/0118071390.jpeg)

:quality(80)/p7i.vogel.de/wcms/77/25/7725cc7179a8901c88f54d63f786f503/0118089114.jpeg)

:quality(80)/p7i.vogel.de/wcms/b8/cb/b8cb90f76a1c9b4641c258c77baa6452/0117870997.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/54/eb54f8523a66b2a8b1a81599213a2849/0118037299.jpeg)

:quality(80)/p7i.vogel.de/wcms/5f/c6/5fc62a91bffb6c673c36722011f8205c/0118076327.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/51/1e513481ef401300756c3bb189188c01/0117631502.jpeg)

:quality(80)/p7i.vogel.de/wcms/4a/c3/4ac36d52b7b85caa24dfb33c6d24dcb3/0116839547.jpeg)

:quality(80)/p7i.vogel.de/wcms/03/f9/03f94da2d43a26f1c5e29951e119dc15/0118070581.jpeg)

:quality(80)/p7i.vogel.de/wcms/c9/22/c9228b8ec955c03dc075e8875f4cabf8/0117754897.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/6f/076f09c7a697f193091a6e6be846aef1/0117862638.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/51/305138abdaeda721646661bf6ac4fdbd/0117756540.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/b9/3cb980e98baaaadddf69a5dad4ad20a0/0117334644.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/4b/794b7d23361d39306753a0abab662274/0117836261.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/88/f388bad02124a8ac7fc5663627838b69/0117819459.jpeg)

:quality(80)/p7i.vogel.de/wcms/2b/cc/2bccc41bb07c895dda4839b927d8c265/0116514416.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/5a/1e5a931b4b81371d6761358130476db5/0117914243.jpeg)

:quality(80)/p7i.vogel.de/wcms/f7/a8/f7a8de2339926d03f6309495bb3e3cdf/0117808261.jpeg)

:quality(80)/p7i.vogel.de/wcms/18/32/1832350986a019c0f74079c2fd03fa28/0117909885.jpeg)

:quality(80)/p7i.vogel.de/wcms/ce/39/ce39b8746f3a7c4fe740dd2ab7ae398e/0117870832.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/5b/435ba2f9a9f3626b158e8c9e21b3ef86/0118068989.jpeg)

:quality(80)/p7i.vogel.de/wcms/16/cc/16cc54cea371a36ebef7a53b952f8516/0118069700.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/21/8b21dc0d8a22fffb04f5a76e1ae7573b/0117948570.jpeg)

:quality(80)/p7i.vogel.de/wcms/2a/7e/2a7efec3a497d5dc95ab215c5d23157d/0118039147.jpeg)

:quality(80)/p7i.vogel.de/wcms/89/14/891466dc6e506808ac85d6d2092a0515/0118057843.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/f4/13f45928ee8acff5534a6c615b4ceef6/0117954493.jpeg)

:quality(80)/p7i.vogel.de/wcms/c2/66/c266c5cfbc51fb7d06557ee079d406bf/0116839110.jpeg)

:quality(80)/p7i.vogel.de/wcms/3a/1a/3a1a267224e51b795ccc6b8df959f18e/0115998041.jpeg)

:quality(80)/p7i.vogel.de/wcms/3d/14/3d1447535880e284712d1daba8d7d466/0115848899.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/56200/56252/65.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/2500/2537/65.jpg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/68800/68851/65.jpg)

:quality(80)/p7i.vogel.de/wcms/5c/e4/5ce49dd49917c29a95bc4c6e7ec0d486/0110632922.jpeg)

:quality(80)/p7i.vogel.de/wcms/2a/4f/2a4f40d489f2679abbd415849e2e35a5/0112237190.jpeg)