# Inductive Adder for the FCC Injection Kicker System

Inductive Adder für das FCC Injektionskickersystem

Zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.) vorgelegte Dissertation von David Gerd Woog, geboren in Northeim, Deutschland Fachbereich Elektrotechnik und Informationstechnik Tag der Einreichung: 03.12.2019, Tag der Prüfung: 04.03.2020

1. Gutachten: Prof. Dr.-Ing. Herbert De Gersem 2. Gutachten: Prof. Dr.-Ing. Gerd Griepentrog Darmstadt – D 17

Inductive Adder for the FCC Injection Kicker System Inductive Adder für das FCC Injektionskickersystem

vorgelegte Dissertation von David Gerd Woog, geboren in Northeim, Deutschland Fachbereich Elektrotechnik und Informationstechnik

Review: Prof. Dr.-Ing. Herbert De Gersem

Review: Prof. Dr.-Ing. Gerd Griepentrog

Date of submission: 03.12.2019 Date of thesis defense: 04.03.2020

Darmstadt – D 17

Bitte zitieren Sie dieses Dokument als: URN: urn:nbn:de:tuda-tuprints-117260 URL: http://tuprints.ulb.tu-darmstadt.de/11726

Dieses Dokument wird bereitgestellt von tuprints, E-Publishing-Service der TU Darmstadt http://tuprints.ulb.tu-darmstadt.de tuprints@ulb.tu-darmstadt.de

Veröffentlicht unter CC BY-SA 4.0 International https://creativecommons.org/licenses/

### Erklärungen laut Promotionsordnung

#### §8 Abs. 1 lit. c PromO

Ich versichere hiermit, dass die elektronische Version meiner Dissertation mit der schriftlichen Version übereinstimmt.

#### §8 Abs. 1 lit. d PromO

Ich versichere hiermit, dass zu einem vorherigen Zeitpunkt noch keine Promotion versucht wurde. In diesem Fall sind nähere Angaben über Zeitpunkt, Hochschule, Dissertationsthema und Ergebnis dieses Versuchs mitzuteilen.

#### §9 Abs. 1 PromO

Ich versichere hiermit, dass die vorliegende Dissertation selbstständig und nur unter Verwendung der angegebenen Quellen verfasst wurde.

#### §9 Abs. 2 PromO

Die Arbeit hat bisher noch nicht zu Prüfungszwecken gedient.

Darmstadt, 03.12.2019

David Woog

### Zusammenfassung

Die vorliegende Dissertation beschreibt die Auslegung, Konstruktion, den Zusammenbau und die Ausmessung eines Inductive Adder (IA) Pulsgenerators. Der IA wurde für die Future Circular Collider (FCC) Studie ausgelegt, um die Möglichkeiten eines höchst zuverlässigen Pulsgenerators für Kickermagnetsysteme in Teilchenbeschleunigern zu erforschen.

Kickermagnete werden in Teilchenbeschleunigern verwendet, um den Teilchenstrahl abzulenken: z.B. bei der Injektion oder Extraktion des Teilchenstrahls in den oder aus dem Orbit eines Zirkularbeschleunigers. Aus verschiedenen Gründen können die Thyratrons, wie sie oft für die Pulsgeneratoren solcher Systeme eingesetzt werden, nicht für das FCC Kickersystem verwendet werden. Daher ist ein alternativer Pulsgenerator mit auf Halbleitern basierenden Schaltern (sog. solid-state Schalter) notwendig.

Halbleiter basierte Schalter sind eine vielversprechende Alternative, um Thyratrons in Pulsed-Power Anwendungen zu ersetzen. Dies wurde möglich, da durch die Weiterentwicklung halbleiterbasierter Bauelemente bezüglich Strom und Spannung in den vergangenen Jahren deutliche Fortschritte erzielt wurden. Die IA Technologie macht es möglich, mit mehreren Lagen und durch Parallelschaltung von solid-state Schaltern einen Pulsgenerator zu bauen, der Pulse mit hohen Spannungs- und Stromwerten erzeugen kann.

Ein IA, der die Injektionsparameter des FCC erfüllen kann, wurde bisher noch nicht gebaut. Daher wurde auf Basis dieser Parameter ein IA ausgelegt. Eine Herausforderung ist die Kombination aus 2.4 kA und 15 kV Ausgangspuls, 2.3  $\mu$ s Pulslänge, 6.25  $\Omega$  Systemimpedanz und die kurze Anstiegszeit von etwa 75 ns (0.5 %-99.5 %) des Ausgangsstroms. Die Spezifikationen der Hauptkomponenten wurden definiert und Beispielkomponenten getestet. Neben Standardkomponenten für MOSFETs und Gatetreiber wurden z.B. für die Pulskondensatoren und Magnetkerne Maßanfertigungen benötigt.

Nach der Komponentenwahl wurden der magnetische Kreis ausgelegt, die Gehäuseteile produziert und der IA zusammengebaut. Um kurze Anstiegszeiten zu erreichen, musste das Design möglichst klein gehalten werden. Durch das Vormagnetisieren der Magnetkerne konnte das erforderliche Magnetmaterial nahezu halbiert und so auch die Höhe des IA verringert werden. Mit einer Ölisolierung konnte die Ausgangsspannung von 15 kV bei den durch die geringe Impedanz von 6.25  $\Omega$  bedingten Spaltmaßen realisiert werden und gleichzeitig die Durchmesser der Magnetkerne klein gehalten werden. Die Funktion von passiver, analoger Modulation konnte auch mit vormagnetisierten Magnetkernen gezeigt werden, was zur Reduzierung des Spannungsabfalls während des Impulses genutzt werden kann. Die geplante Ausgangsspannung von 15 kV konnte für einen Lastwiderstand von 50  $\Omega$  bei einer Impulslänge von 2.32 µs erfolgreich getestet werden. Auch der geplante Lagenausgangsstrom von 2.4 kA konnte bei der nominellen Lagenspannung von 1 kV erreicht werden.

Außerdem wurde ein Ansatz vorgestellt, der den Einsatz eines IA innerhalb eines Pulssystems mit Kurzschlussterminierung möglich macht. Dabei wurde mit Simulationen gezeigt, dass die Stromerhöhung im Schaltelement vermieden werden kann, wenn durch das Schalten eines zweiten Schaltelements die Pulsimpedanz des IA verändert wird.

Die Herausforderungen des FCC Injektionssystems können mit den in dieser Dissertation gezeigten Methoden wie z.B. Siliziumkarbid MOSFETs, Ölisolierung, vormagnetisierten Magnetkernen und analoger Modulation bewältigt werden. Manche Verbesserungsmöglichkeiten des Designs, die sich im Laufe der Arbeit gezeigt haben, sind hervorgehoben und mögliche Lösungen werden diskutiert.

Diese Arbeit ermöglicht die Entwicklung eines IA für die Anforderungen des FCC Injektionskickersystems bei hohen Frequenzen, wie sie für einen so langen Zirkularbeschleuniger mit entsprechend vielen Vorbeschleunigern notwendig sind. Die Errungenschaften der Arbeit erlauben außerdem den Einsatz eines IA, um Pulsgeneratoren in bestehenden Teilchenbeschleunigern am CERN zu ersetzen. Hier hat der IA besonders durch den Einsatz von halbleiterbasierten Schaltern und sein kompaktes Design ohne SF6-Gas isolierte Komponenten oder Thyratrons Vorteile.

### Abstract

This thesis presents the design, construction, assembly and measurements of an inductive adder (IA) type pulse generator. The IA was built for the future circular collider (FCC) study to investigate the possibility of a fast, high current, high voltage and reliable pulse generator for use in the injection kicker systems. In addition, the possibility of utilizing this technology as part of the injection system of an existing particle accelerator, with a generator voltage of up to 40 kV, is born in mind during the studies for the FCC injection IAs.

Kicker magnets are used in particle accelerators to deflect the beam for example during the injection process, to place the injected beam onto the central orbit of a circular accelerator. In order to achieve a high reliability for the FCC, it is necessary to replace the thyratrons presently used in the pulse generators of the kickers systems by pulse generators based on solid-state technology.

Solid-state switches are a promising alternative to thyratrons for pulsed power applications. Recent developments have increased the current and voltage ratings of power semiconductors and make it possible to use them for high current and voltage solid state pulse generators. The IA is a promising technology for generating high voltage and high current pulses: it consists of many ground-referenced layers, to achieve the high voltage, and many parallel connected solid state switches to achieve the high current capability.

An IA with demanding specifications as required for the FCC injection kicker system has never been built so far. The main challenge for such an IA is the combination of 2.4 kA and 15 kV output waveform, 2.3  $\mu$ s flattop duration, 6.25  $\Omega$  system impedance and a short current rise time of approximately 75 ns (0.5 %-99.5 %). Based on these demanding requirements, an inductive adder was designed and simulated. The specifications for the main components of the IA were defined and sample components were ordered and tested. In addition to off-the-shelf components, such as SiC MOSFETs and gate drivers, some components required a custom made design e.g. pulse capacitors and magnetic cores.

After the components were selected, based on detailed analyses of tests and measurements, the hardware structure was designed and manufactured and a prototype IA was assembled. To obtain fast rise times, the height of the mechanical structure was reduced, by applying biasing to the magnetic cores, which made it possible to decrease the required volume of magnetic material in half. An oil insulation was selected to insulate the 15 kV output voltage and realise the low characteristic impedance of  $6.25 \Omega$  while keeping the diameter of the magnetic cores within an acceptable range. The principle of passive analogue modulation, together with biasing to reduce the flattop droop was proven. The required output voltage of 15 kV was achieved for a load impedance of  $50 \Omega$  with a pulse length of  $2.32 \mu$ s. The specified layer output current of 2.4 kA was demonstrated with the nominal layer output voltage of 1 kV.

Furthermore, a theoretical approach to use the IA in a short-circuit terminated system is discussed. Simulations show that the increase of the current due to pulse reflection from a short-circuit can be prevented by adding a second switch in each branch of the IA to change the impedance of the stack. The demanding requirements of the FCC injection system can be achieved by using the IA with presented technologies such as SiC MOSFETs, oil insulation, magnetic core biasing and passive analogue modulation. Some issues which require future work are discussed and possible improvements are proposed.

### Contents

| Lis | of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                        | xiv                                                                                                                    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Lis | of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                         | xv                                                                                                                     |

| Lis | of Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                  | xvii                                                                                                                   |

| Lis | of Symbols                                                                                                                                                                                                                                                                                                                                                                                                                                        | xix                                                                                                                    |

| Lis | of Subscripts                                                                                                                                                                                                                                                                                                                                                                                                                                     | xxi                                                                                                                    |

| 1   | Introduction and Motivation                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                      |

| 2   | Fast pulsed systems         2.1       Injection and extraction systems                                                                                                                                                                                                                                                                                                                                                                            | <b>5</b><br>7<br>8<br>9<br>9                                                                                           |

|     | <ul> <li>2.4.2 Marx generator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                           | 10<br>11<br>12<br>13<br>13<br>13                                                                                       |

| 3   | anductive adder principle         3.1       Advantages and disadvantages         3.2       Existing inductive adders         3.2.1       Difference to transmission line adder         3.3       Equivalent circuit of the inductive adder         3.4       Design optimisation of the key components         3.4.1       Insulation         3.4.2       Transformer core         3.4.3       Primary circuit         3.5       Modulation layer | <ol> <li>15</li> <li>17</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> <li>24</li> <li>27</li> <li>28</li> </ol> |

| 4   | Design of the FCC inductive adder4.1 System requirements                                                                                                                                                                                                                                                                                                                                                                                          | <b>31</b><br>31                                                                                                        |

|    | 4.2                                     | Design choices for the prototype                                      | 32                                      |

|----|-----------------------------------------|-----------------------------------------------------------------------|-----------------------------------------|

|    |                                         | 4.2.1 Insulation design                                               | 33                                      |

|    |                                         | 4.2.2 Magnetic core design                                            | 35                                      |

|    |                                         | 4.2.3 Capacitor design                                                | 35                                      |

|    | 4.3                                     | Simulation in PSpice                                                  | 37                                      |

|    |                                         | 4.3.1 Simulation results                                              | 41                                      |

|    |                                         | 4.3.2 Influence of parasitic capacitance of coaxial geometry          | 42                                      |

|    | 4.4                                     |                                                                       | 44                                      |

| 5  | Fau                                     | It conditions                                                         | 47                                      |

|    | 5.1                                     | System protection methods in fault case                               | 48                                      |

|    | 5.2                                     | Fast switch-off in case of core saturation                            | 48                                      |

|    | 5.3                                     | System protection for biasing circuit                                 | 48                                      |

|    | 5.4                                     |                                                                       | 48                                      |

| 6  | Mea                                     | asurements on components                                              | 51                                      |

|    | 6.1                                     | Magnetic cores                                                        | 51                                      |

|    |                                         | 6.1.1 Measurement of pulsed magnetizing current                       | 51                                      |

|    |                                         | 6.1.2 BH-curve measurement                                            | 54                                      |

|    | 6.2                                     | Semiconductor switches                                                | 56                                      |

|    |                                         | 6.2.1 Radiation hardness of SiC components                            | 57                                      |

|    | 6.3                                     | Capacitors                                                            | 58                                      |

|    | 6.4                                     | Diode                                                                 | 59                                      |

|    | 6.5                                     | Printed circuit board                                                 | 59                                      |

| 7  | Ass                                     | sembly of the prototype                                               | 61                                      |

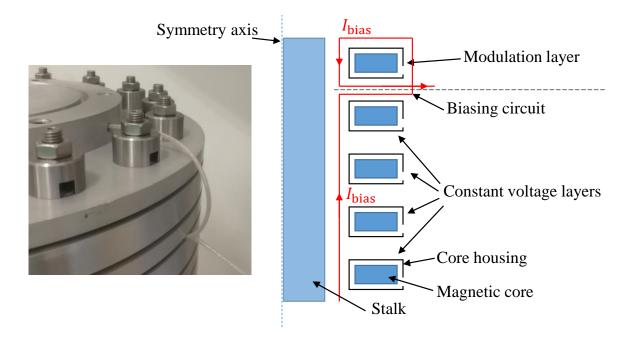

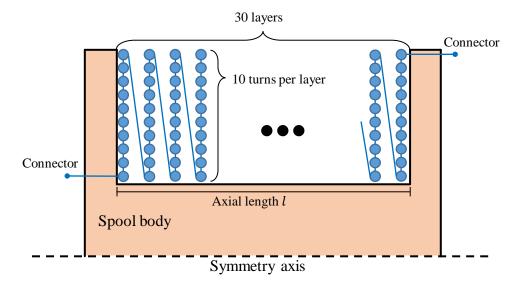

|    | 7.1                                     | Transformer stack                                                     | 61                                      |

|    | 7.2                                     | Printed circuit boards (PCBs)                                         | 64                                      |

|    | 7.3                                     | Full-scale prototype assembly                                         | 66                                      |

|    |                                         | 7.3.1 Expected manufacturing tolerances                               | 68                                      |

| 8  | Mea                                     | asurements on the prototype                                           | 71                                      |

|    | 8.1                                     | Network analyzer measurements                                         |                                         |

|    | 8.2                                     |                                                                       | 73                                      |

|    |                                         |                                                                       | 74                                      |

|    | 8.3                                     | 5 1 51                                                                | 75                                      |

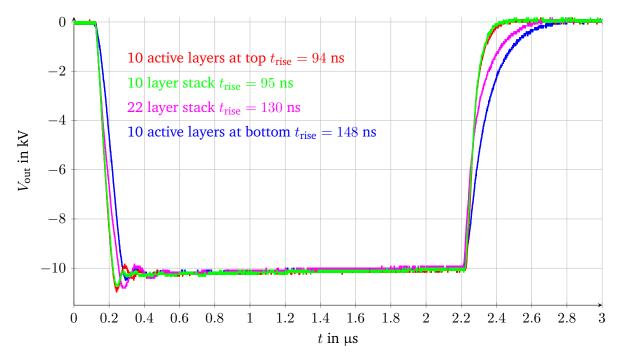

|    | 0 1                                     | Measurements on the 22 layer prototype                                | 77                                      |

|    | 8.4                                     |                                                                       | //                                      |

|    | 8.4                                     | 8.4.1 Consideration of layer position in the stack                    | 79                                      |

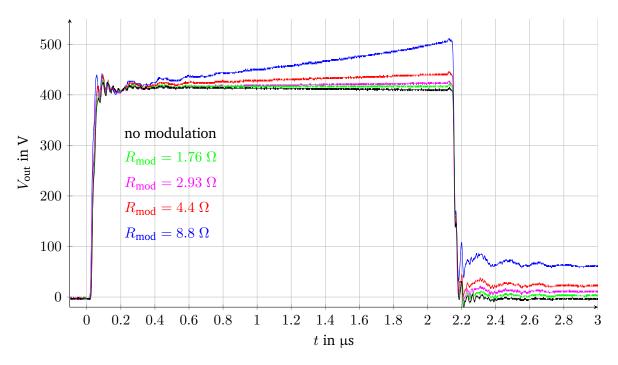

|    | 8.4<br>8.5                              | 8.4.1 Consideration of layer position in the stack                    |                                         |

| 9  | 8.5                                     | 8.4.1 Consideration of layer position in the stack                    | 79                                      |

| 9  | 8.5                                     | <ul> <li>8.4.1 Consideration of layer position in the stack</li></ul> | 79<br>80<br><b>85</b><br>85             |

| 9  | 8.5<br><b>Indu</b><br>9.1<br>9.2        | 8.4.1 Consideration of layer position in the stack                    | 79<br>80<br><b>85</b><br>85<br>85       |

| 9  | 8.5<br><b>Indu</b><br>9.1               | 8.4.1 Consideration of layer position in the stack                    | 79<br>80<br><b>85</b><br>85             |

|    | 8.5<br><b>Indu</b><br>9.1<br>9.2<br>9.3 | 8.4.1 Consideration of layer position in the stack                    | 79<br>80<br><b>85</b><br>85<br>85       |

| 10 | 8.5<br>Indu<br>9.1<br>9.2<br>9.3<br>Con | 8.4.1 Consideration of layer position in the stack                    | 79<br>80<br><b>85</b><br>85<br>85<br>85 |

| A   | Арре | endix                                          | 103 |

|-----|------|------------------------------------------------|-----|

|     | A.1  | Measurement equipment                          | 103 |

|     |      | A.1.1 BH-curve measurements                    | 103 |

|     | A.2  | Supplier for sample components                 | 104 |

|     | A.3  | Design of the air coil for the biasing circuit | 105 |

| Ack | เทกพ | ledgments                                      | 107 |

## List of Figures

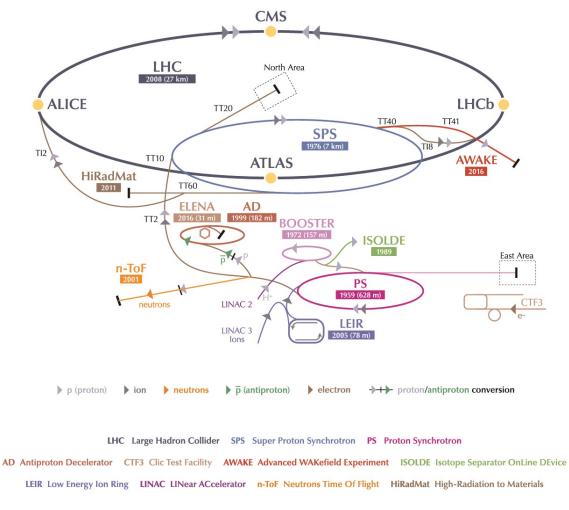

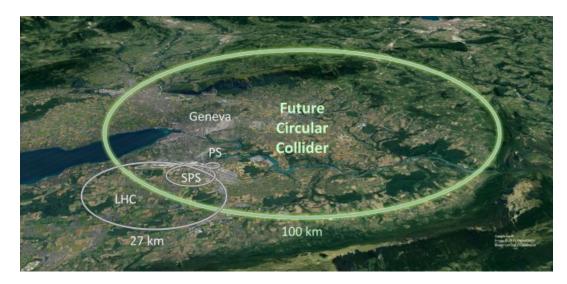

| 1.1<br>1.2   | The CERN accelerator complex                                                                  | 2<br>3  |

|--------------|-----------------------------------------------------------------------------------------------|---------|

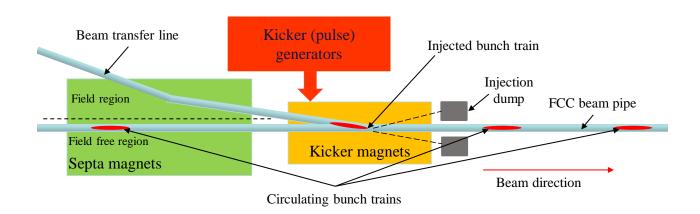

| $2.1 \\ 2.2$ | Schematic of an injection system with kicker magnet and septum magnet                         | 6<br>6  |

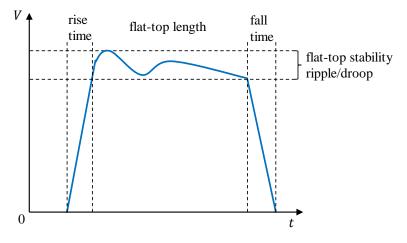

| 2.2<br>2.3   | Definition of pulse parameters                                                                | 8       |

| 2.3<br>2.4   | Schematic drawing of a kicker system with PFN or PFL                                          | 0<br>10 |

| 2.4<br>2.5   | Reels of pulse forming line of the KFA45 pulse generator and high voltage thyratron           | 10      |

| 2.5          | Schematic of a Marx generator                                                                 | 10      |

| 2.0          | Schematic of a Blumlein generator                                                             | 11      |

| 2.7          | Schematic of a transmission line adder                                                        | 12      |

| 2.0          |                                                                                               | 12      |

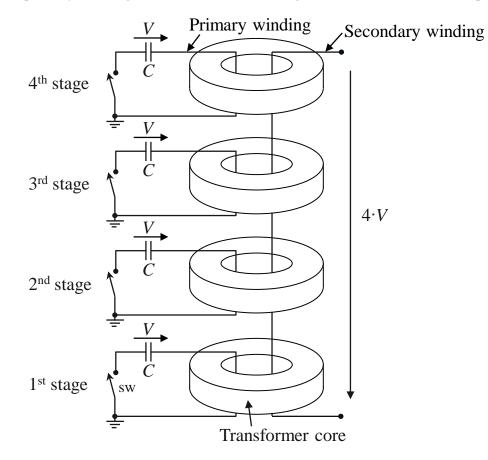

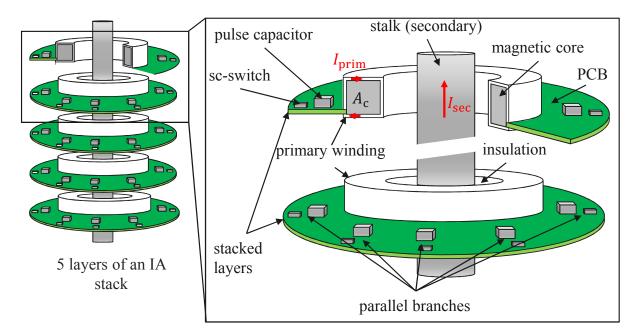

| 3.1          | Simplified drawing of a 4-stage inductive adder                                               | 15      |

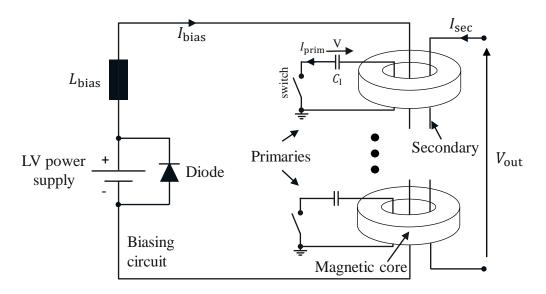

| 3.2          | Schematic drawing of an inductive adder                                                       | 16      |

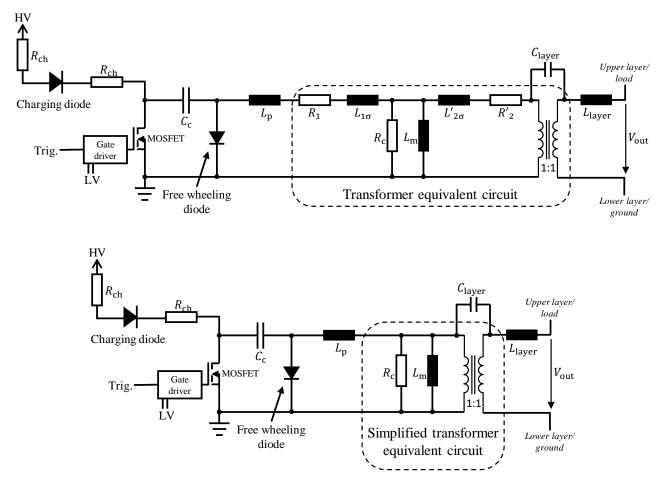

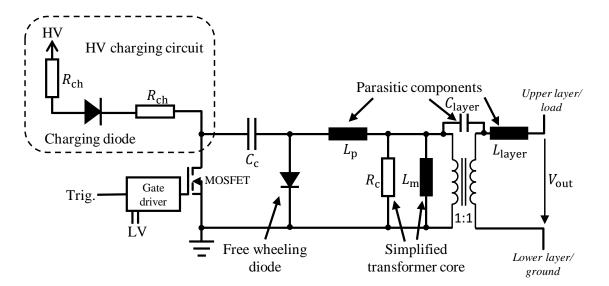

| 3.3          | Simplification of the euivalent circuit of one layer                                          | 19      |

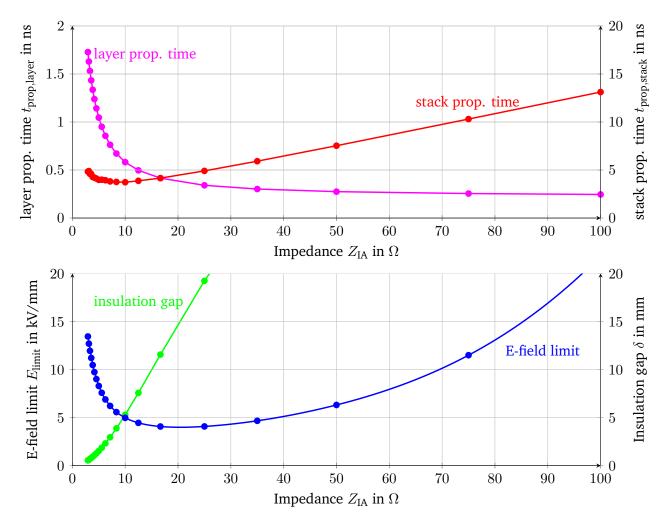

| 3.4          | Calculated propagation time, maximum electric field and insulation gap size over system       |         |

|              | impedance for a given layer voltage and output current                                        | 23      |

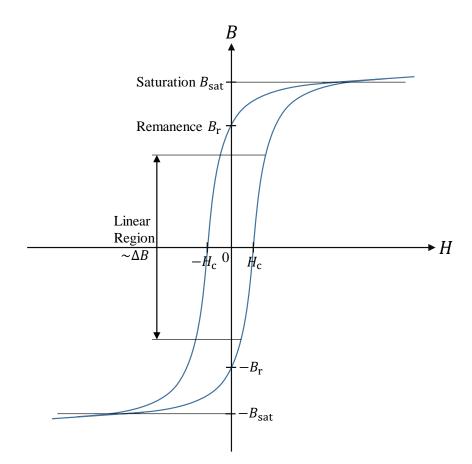

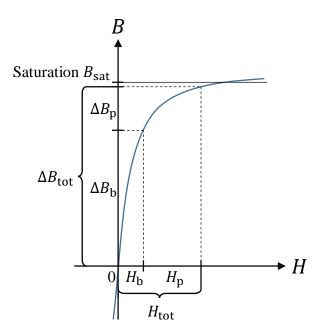

| 3.5          | Example for a BH-characteristic of a magnetic material                                        | 25      |

| 3.6          | Schematic of the biasing circuit                                                              | 26      |

| 3.7          | Equivalent circuit of an IA layer                                                             | 28      |

| 3.8          | Equivalent circuit of a passive and an active analogue modulation layer                       | 29      |

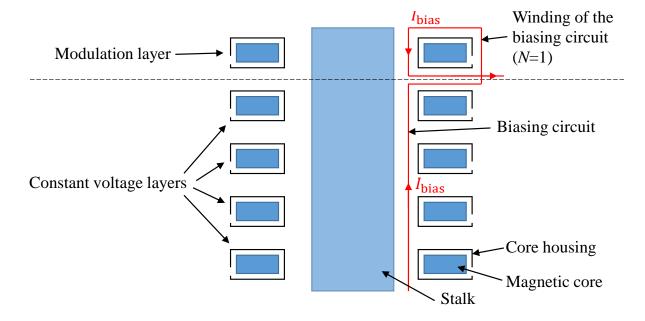

| 3.9          | Biasing circuit location in case of an IA with modulation layer                               | 30      |

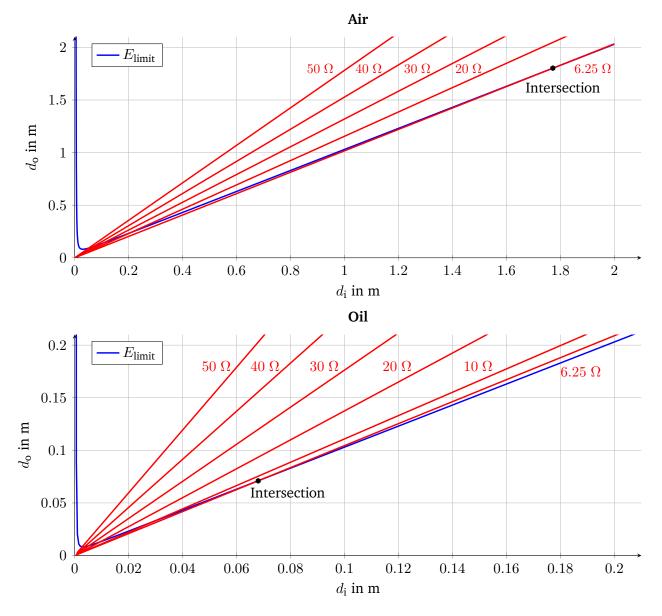

| 4.1          | Calculated design limits for air and oil insulation                                           | 34      |

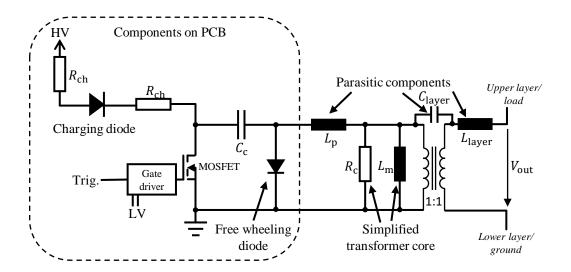

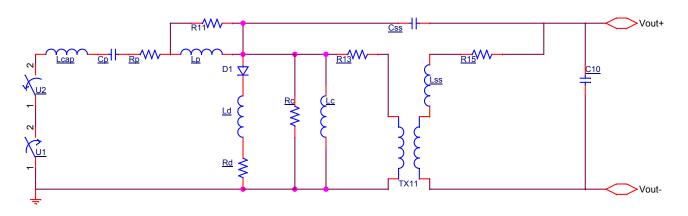

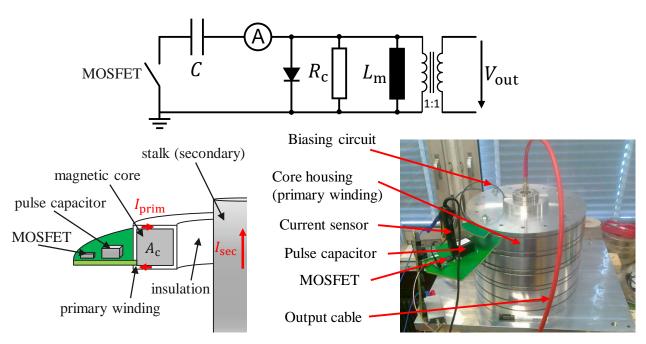

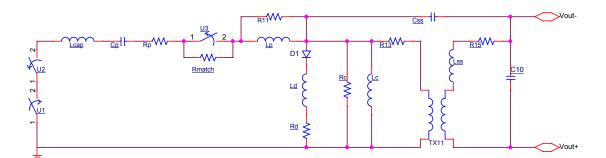

| 4.2          | PSpice model of a constant voltage layer                                                      | 37      |

| 4.3          | PSpice model of a constant voltage layer using the manufacturer MOSFET model                  | 39      |

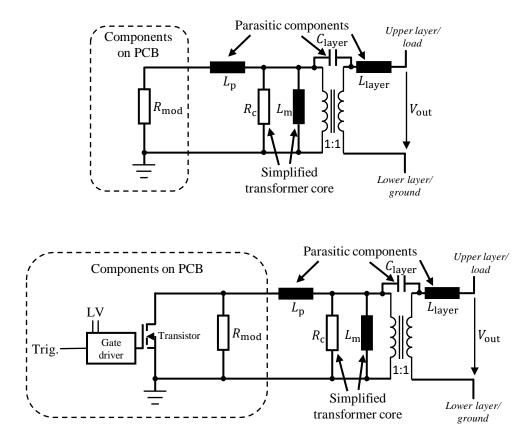

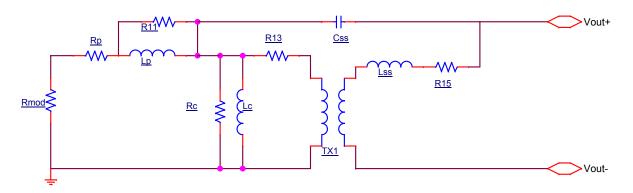

| 4.4          | PSpice model of a passive analogue modulation layer                                           | 40      |

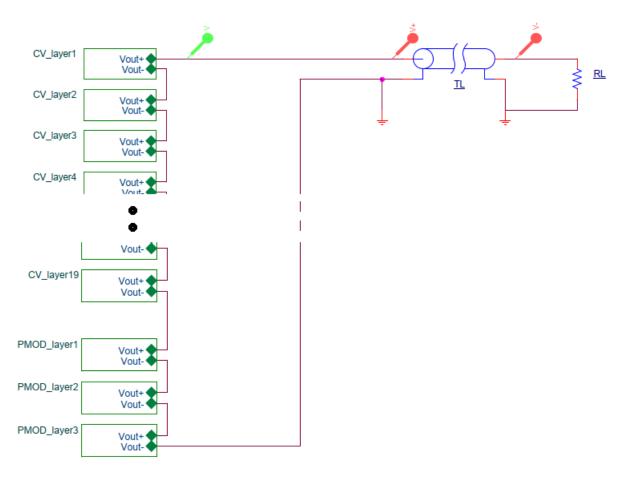

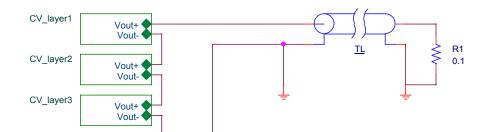

| 4.5          | PSpice model of the 22 layer IA stack                                                         | 40      |

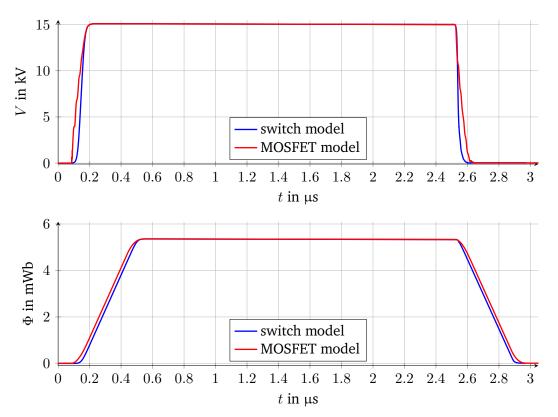

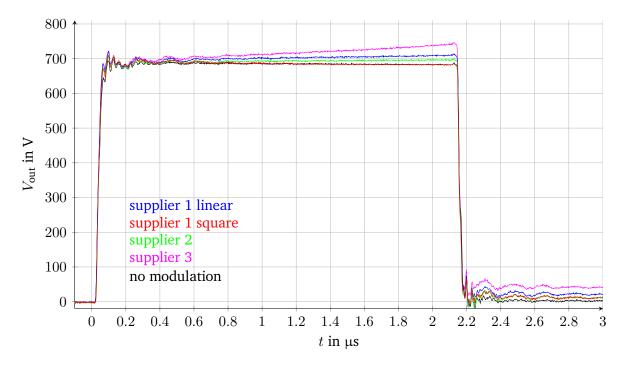

| 4.6          | Simulated output voltage and magnet field of the kicker system modelled in PSpice             | 41      |

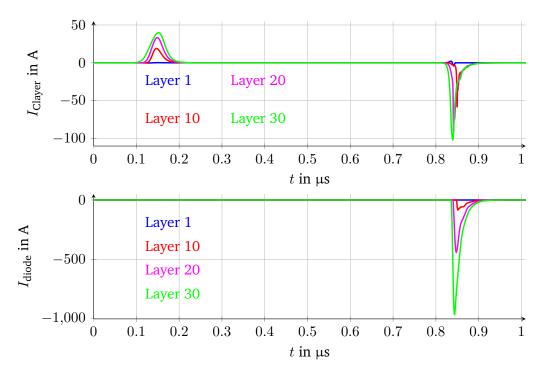

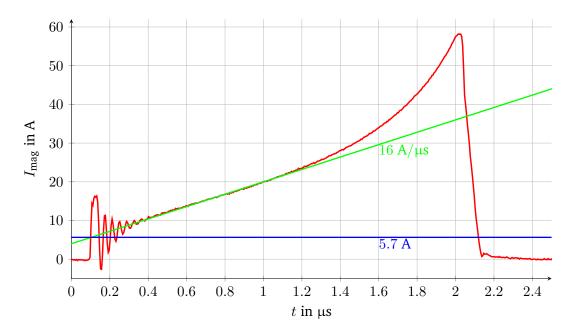

| 4.7          | Example for the simulated current through the parasitic capacitor and the free wheeling diode | 44      |

| 6.1          | Equivalent circuit, schematic drawing and test setup to measure the magnetizing current of    |         |

|              | a magnetic core                                                                               | 51      |

| 6.2          | Primary current decomposed into a core loss current and a magnetizing current                 | 52      |

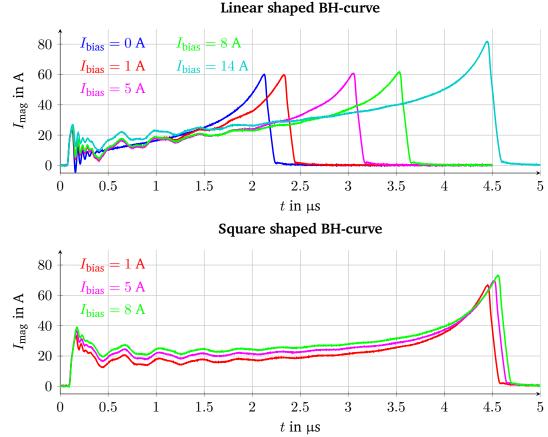

| 6.3          | Measured magnetising current of sample magnetic cores with linear and square shaped           |         |

|              | BH-curve                                                                                      | 53      |

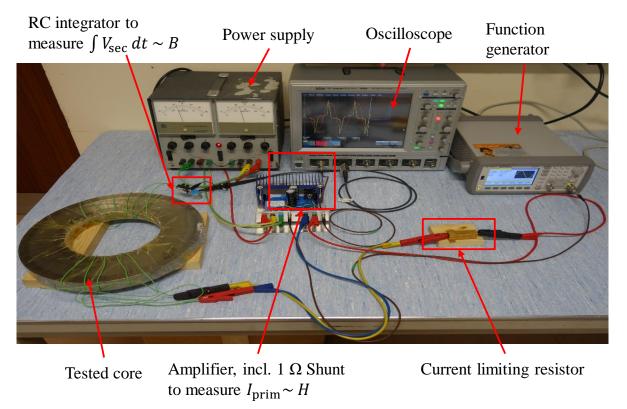

| 6.4          | Test setup for BH-curve measurement on the sample cores                                       | 54      |

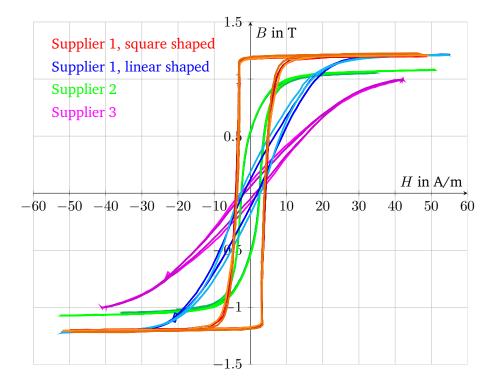

| 6.5          | Measured BH-curves of the sample cores at 500 Hz                                              | 56      |

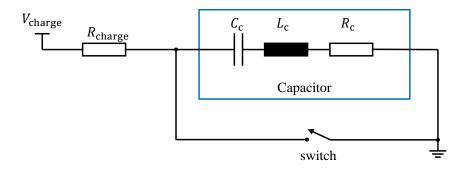

| 6.6          | Lumped element schematic of the capacitor measurement setup                                   | 58      |

|              |                                                                                               |         |

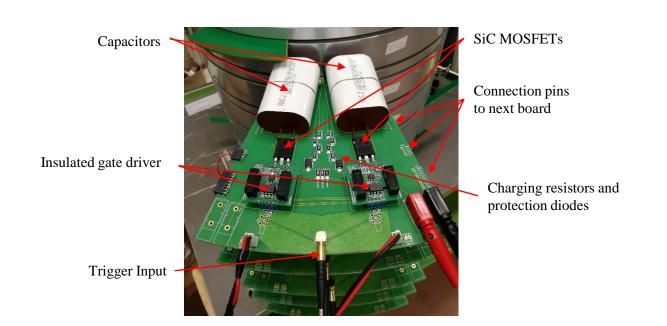

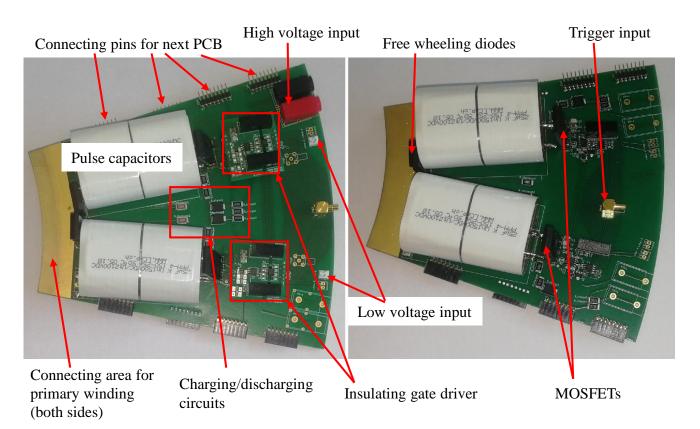

| 6.7        | PCB for the inductive adder prototype                                                                                                                                         | 59  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

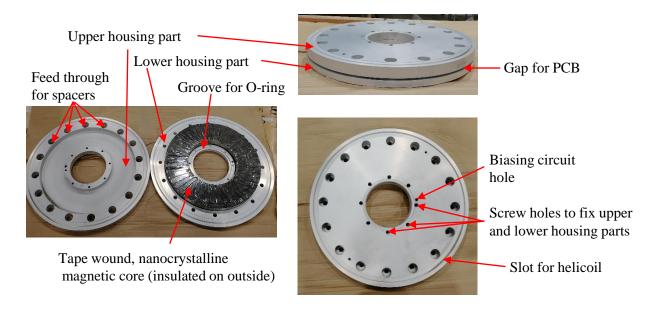

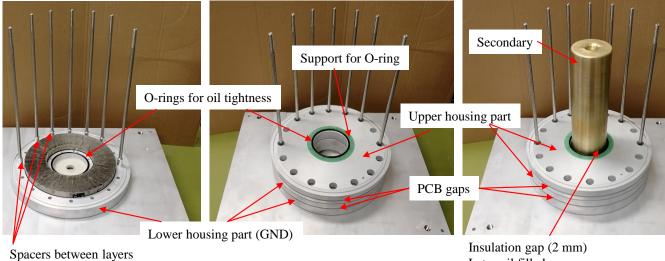

| 7.1        | Assembly of the two housing parts and the insulated, nanocrystalline tape wound core                                                                                          | 61  |

| 7.2        | Assembly of the stack                                                                                                                                                         | 62  |

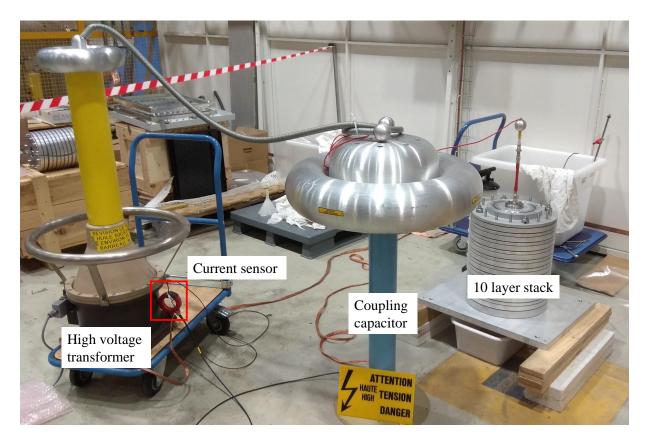

| 7.3        | Test setup for the partial discharge and breakthrough measurements                                                                                                            | 63  |

| 7.4        | The PCB with two parallel branches of the primary circuit                                                                                                                     | 65  |

| 7.5        | Schematic of one IA layer including charging resistors and diode                                                                                                              | 66  |

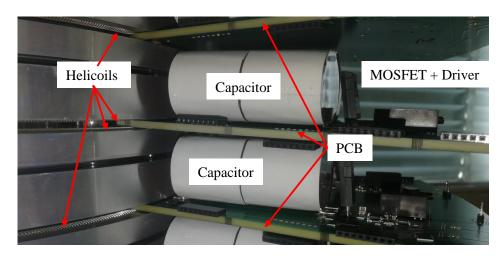

| 7.6        | Connection of the PCBs to the primary winding with helicoils                                                                                                                  | 67  |

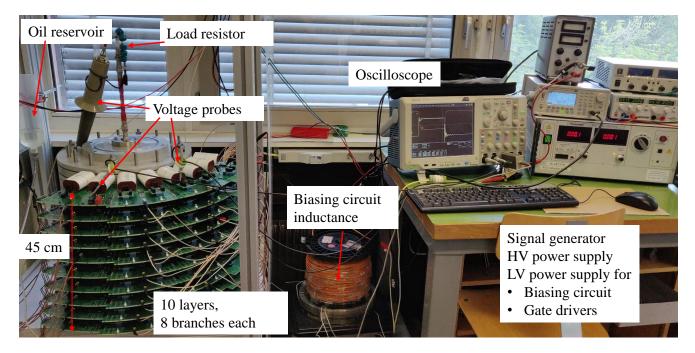

| 7.7        | Test bench of the 10 layer prototype IA                                                                                                                                       | 67  |

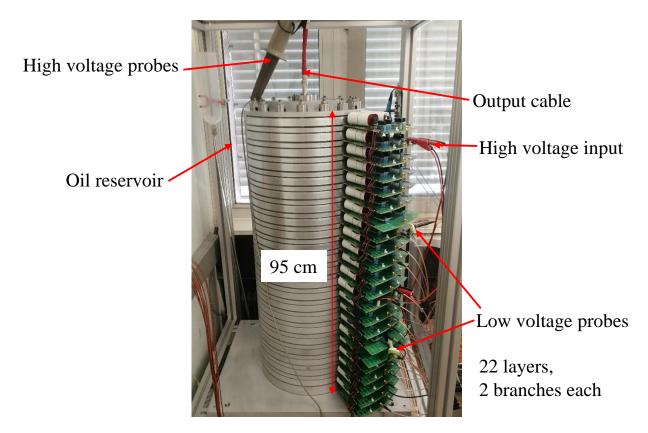

| 7.8        | The 22 layer prototype IA                                                                                                                                                     | 68  |

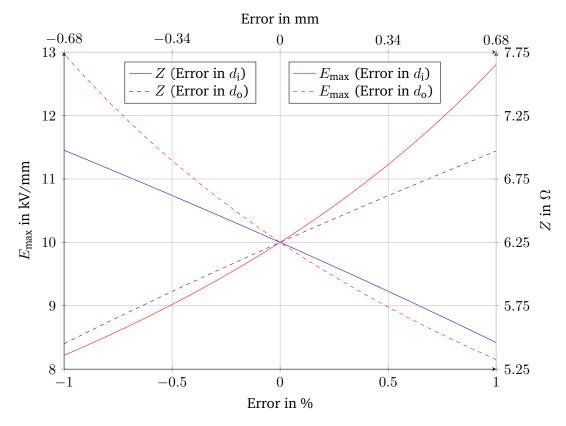

| 7.9        | Calculated influence of a manufacturing error of the inner or outer insulation diameter                                                                                       | 69  |

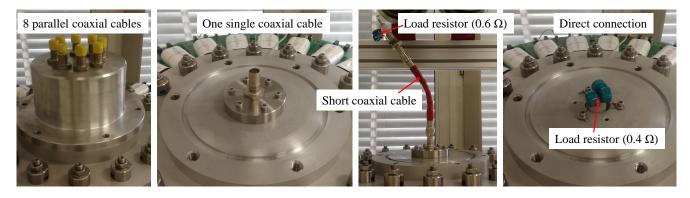

| 7.10       | Connection of the load resistor to the output of the IA                                                                                                                       | 69  |

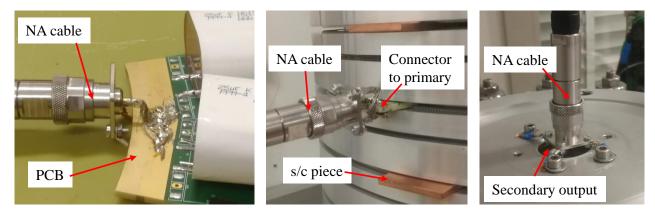

| 8.1        | Connection of the network analyzer cable to the PCB, primary and secondary of the IA                                                                                          | 72  |

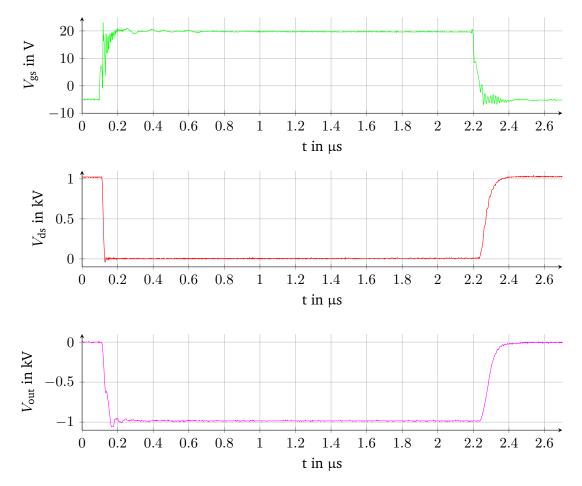

| 8.2        | Example of meaured gate-source, drain-source and output voltage waveforms                                                                                                     | 73  |

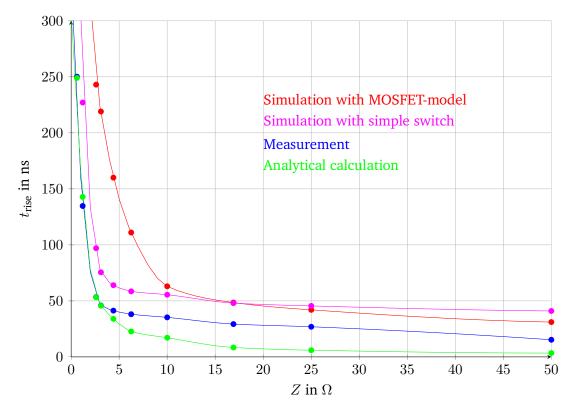

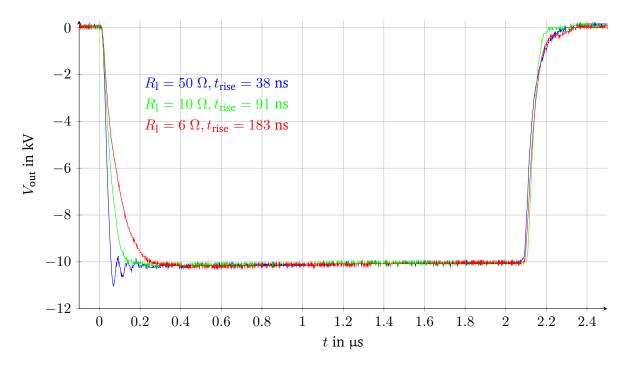

| 8.3        | Output waveform rise time with one layer for different load resistors                                                                                                         | 74  |

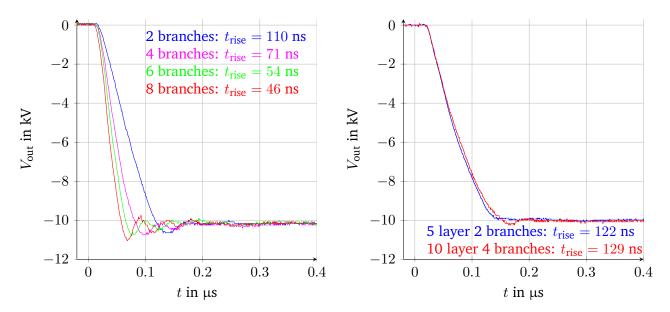

| 8.4        | Measured output waveform rise time for different number of parallel branches                                                                                                  | 75  |

| 8.5        | Measured output voltage of the 10 layer prototype with 8 branches                                                                                                             | 76  |

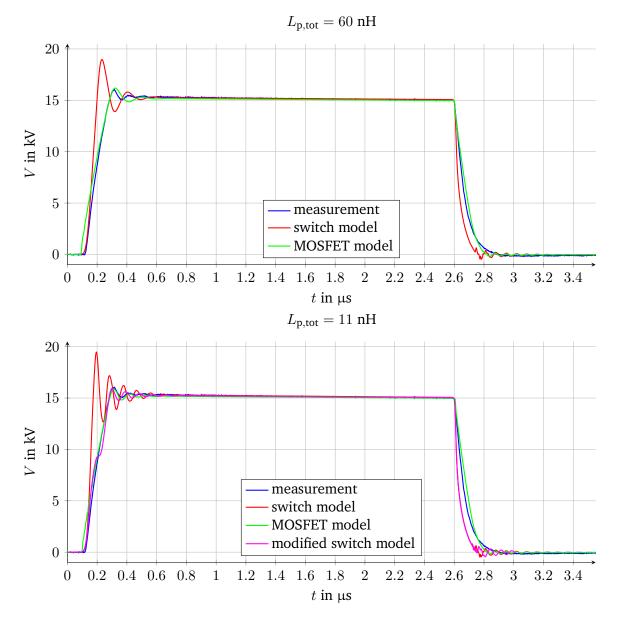

| 8.6        | Comparison of the measured and simulated output waveform                                                                                                                      | 78  |

| 8.7<br>8.8 | Comparison of the measured 10 kV output waveforms with different IA topologies The biasing circuit of the modulation layer and a schematic describing the path of the biasing | 79  |

| 0.0        | loop                                                                                                                                                                          | 81  |

| 8.9        | Measured output waveform of the IA for different modulation resistors and a given magnetic                                                                                    |     |

| 8.10       | core                                                                                                                                                                          | 81  |

|            | resistor                                                                                                                                                                      | 83  |

| 9.1        | PSpice model of an IA layer with additional resistor and switch to match the impedance of                                                                                     |     |

|            | the stack                                                                                                                                                                     | 86  |

| 9.2        | PSpice model of an IA stack connected to a ideal transmission line, representing the kicker                                                                                   |     |

|            | magnet with a short-circuit at the end                                                                                                                                        | 87  |

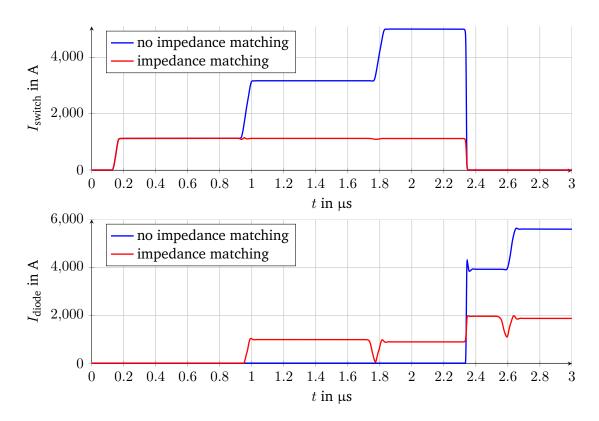

| 9.3        | Simulated current of switch and diode with and without impedance matching                                                                                                     | 87  |

| A.1        | Required flux density swing in biasing inductance                                                                                                                             | 105 |

| A.2        | Winding scheme of the air coil for the biasing inductance                                                                                                                     | 106 |

### **List of Tables**

| 2.1                             | Comparison of injection kicker systems of the CERN accelerator complex                                                                                                                                                      | 7                 |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 3.1                             | Selection of existing inductive adders                                                                                                                                                                                      | 18                |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5 | FCC injection parameters with LHC as HEB at 3.3 TeVFCC injection kicker parameters with LHC as HEBDesign parameter for the inductive adder prototypeComponent parameters for the PSpice simulationPSpice simulation results | 32<br>37          |

| 5.1<br>5.2                      | Summary of possible fault conditions                                                                                                                                                                                        | 47<br>49          |

| 6.1<br>6.2<br>6.3               | Sample cores with measured values                                                                                                                                                                                           |                   |

| 7.1                             | Calculated and measured breakdown voltage $V_{\rm bd}$ of the IA insulation with air or oil $\ldots$                                                                                                                        | 64                |

| 8.1<br>8.2<br>8.3               | Results of the inductance measurements with a network analyzer                                                                                                                                                              | 79                |

| A.1<br>A.2<br>A.3<br>A.4<br>A.5 | Equipment used for measurments on the IA components and on the IA prototype<br>Equipment used for measurments on the IA components and on the IA prototype<br>Supplier and material information of sample magnetic cores    | 103<br>104<br>104 |

### **List of Abbreviations**

| ALS-U<br>bd | advanced light source upgrade<br>breakdown           |

|-------------|------------------------------------------------------|

| С           | capacitor                                            |

| CERN        | European organization for nuclear research           |

| CLIC        | compact linear collider                              |

| CV          | constant voltage                                     |

| DARHT       | dual-axis radiographic hydrodynamic test facility    |

| DC          | direct current                                       |

| DNA         | deoxyribonucleic acid                                |

| DR          | damping ring                                         |

| FCC         | future circular collider                             |

| GaN         | gallium nitride                                      |

| GTO         | gate turn-off thyristor                              |

| HEB         | high energy booster                                  |

| HEH         | high energy hadron                                   |

| hh          | hadron-hadron                                        |

| HV          | high voltage                                         |

| IA          | inductive adder                                      |

| ID          | inner diameter                                       |

| IVA         | inductive voltage adder                              |

| IGBT        | integrated gate bipolar transistor                   |

| KFA45       | injection kicker system of the PS                    |

| L           | inductor                                             |

| LBNL        | Lawrence Berkeley national laboratory                |

| LHC         | large hadron collider (particle accelerator at CERN) |

| LLNL        | Lawrence Livermore national laboratory               |

| LTD         | linear transformer driver                            |

| LV          | low voltage                                          |

| MKI         | injection kicker system of the LHC                   |

| MKP         | injection kicker system of the SPS                   |

| MOD         | modulation                                           |

| MOSFET      | metal oxide semiconducting field effect transistor   |

| OD          | outer diameter                                       |

| PCB         | printed circuit board                                |

| PFL         | pulse forming line                                   |

| PFN         | pulse forming network                                |

| PS          | proton synchrotron (particle accelerator at CERN)    |

| R           | resistor                                             |

|             |                                                      |

| RCPS | resonant charging power supply                          |

|------|---------------------------------------------------------|

| rep  | repetition                                              |

| RF   | radio frequency                                         |

| RMS  | root mean square                                        |

| SC   | semiconductor                                           |

| SEB  | single event burnout                                    |

| SEE  | single event effect                                     |

| SF6  | sulfur hexafluoride                                     |

| SG   | spark gap                                               |

| Si   | silicon                                                 |

| SiC  | silicon carbide                                         |

| SPS  | super proton synchrotron (particle accelerator at CERN) |

| SW   | switch                                                  |

| TDI  | target dump injection                                   |

| Trig | trigger                                                 |

## **List of Symbols**

| A                      | m <sup>2</sup> | area                               |

|------------------------|----------------|------------------------------------|

| $A_{c}$                | $m^2$          | actual cross section               |

| $A_{\rm Fe}$           | $m^2$          | effective cross section            |

| B B                    | T              | magnetic flux density              |

| $B_{\rm r}$            | T<br>T         | e .                                |

| -                      | T<br>T         | remanence flux density             |

| $B_{sat}$              |                | saturation flux density            |

| C                      | F              | capacity                           |

| $C_{b}$                | F              | branch capacity                    |

| $C_1$                  | F              | layer capacity                     |

| $C_{\text{layer}}$     | F              | parasitic capacitance of one layer |

| D                      | $As/m^2$       | electric flux density              |

| d                      | m              | diameter                           |

| E                      | V/m            | electric field strength            |

| $E_{\max}$             | V/m            | maximum electric field strength    |

| f                      | Hz             | frequency                          |

| H                      | A/m            | magnetic field strength            |

| h                      | m              | height                             |

| Ι                      | А              | electric current                   |

| i                      | -              | index of summation                 |

| Iout                   | А              | output current                     |

| I <sub>prim</sub>      | А              | primary current                    |

| I <sub>sec</sub>       | А              | secondary current                  |

| J                      | $A/m^2$        | electric current density           |

| l                      | m              | length                             |

| L                      | Н              | inductance                         |

| $L_{\text{bias}}$      | Н              | biasing inductance                 |

| $L_{\text{layer}}$     | Н              | parasitic inductance of one layer  |

| l <sub>m</sub>         | m              | magnetic path length               |

| $L_{\rm m}$            | m              | mutual inductance                  |

| $L_{\rm p}$            | Н              | primary inductance of one layer    |

| Ň                      | -              | total number of layers             |

| $n_{\rm branch}$       | -              | number of branche                  |

| $n_{\text{layer}}$     | _              | number of layer                    |

| Q                      | С              | electric charge                    |

| r                      | m              | radius                             |

| $\stackrel{\prime}{R}$ | Ω              | resistance                         |

| $R_{\rm mod}$          | $\Omega$       | modulation resistance              |

| S                      | -              | scattering parameter               |

| 5                      |                | seattering parameter               |

| t                    | S     | time                               |

|----------------------|-------|------------------------------------|

| $t_{prop}$           | S     | porpagation time                   |

| $\dot{V}$            | V     | voltage                            |

| $V_{\rm out}$        | V     | output voltage                     |

| w                    | m     | width                              |

| Z                    | Ω     | impedance                          |

| $Z_{\mathrm{IA}}$    | Ω     | characteristic impedance of the IA |

|                      |       |                                    |

| $\delta$             | m     | insulation gap                     |

| ε                    | As/Vm | permittivity                       |

| $\varepsilon_0$      | As/Vm | permittivity of vacuum             |

| $\varepsilon_{ m r}$ | -     | relative permittivity              |

| $\eta_{ m Fe}$       | -     | fill factor                        |

| $\mu$                | Vs/Am | permeability                       |

| $\mu_0$              | Vs/Am | permeability of vacuum             |

| $\mu_{ m r}$         | -     | relative permeability              |

| $\Psi$               | Wb    | magnetic flux                      |

|                      |       |                                    |

## List of Subscripts

| b        | bias                   |

|----------|------------------------|

| bd       | break down             |

| bias     | biasing                |

| branch   | parallel branch        |

| c        | magnetic core          |

| cap      | capacitor              |

| ch       | charging               |

| coax     | coaxial                |

| CVlayer  | constant voltage layer |

| f        | fall                   |

| i        | inner                  |

| ins      | insulation             |

| int      | integrator             |

| IA       | inductive adder        |

| 1        | load                   |

| layer    | stacked layer          |

| m        | magnetizing            |

| max      | maximum value          |

| MODlayer | modulation layer       |

| 0        | outer                  |

| out      | output                 |

| р        | primary, pulse         |

| prop     | propagation            |

| r        | rise                   |

| S        | stage                  |

| SS       | secondary stray        |

| tor      | toroidal               |

| tot      | total                  |

| Z        | in axial direction     |

|          |                        |

| $\sigma$ | stray parameter        |

|          |                        |

### **1 Introduction and Motivation**

In 1954 the European Organization for Nuclear Research (CERN) was founded and located in the area of Geneva. Scientists and researchers from the 22 member states and from all over the world are pushing the limits of physics to improve our understanding of the world we live in. Important and powerful tools for this research are particle accelerators and colliders which can accelerate particles to nearly the speed of light and collide them. Over the years of CERN's existence several particle accelerators have been built and used. The Large Hadron Collider (LHC), currently the biggest and most powerful particle accelerator in the world, was finished in 2008. Even if the LHC is the largest accelerator it is anyway only the last piece of a long acceleration chain consisting of many particle accelerators are needed. In Fig. 1.1 the CERN accelerator complex is shown. It can be seen that many machines of different sizes are accelerating different particle types for a diverse range of experiments.

The LHC with a nominal centre of mass energy of 14 TeV (7 TeV for each of the counter rotating beams) has a planned operation time span until 2035. Design, component construction, final assembly and startup of the LHC took around 30 years [20]. With this background it is obvious that the planning of an accelerator for the post LHC time should already start shortly after the LHC commissioning. For this reason a design study for a future circular collider (FCC) with a centre of mass energy of 100 TeV started in 2013. The FCC study investigates the challenges of a 100 TeV centre-of-mass energy hadron-hadron (hh) collider in the Geneva region. The proposed location of the FCC accelerator is shown in Fig. 1.2.

A big challenge from the technological point of view will be the injection of the particle beams from the pre-accelerator, also called high energy booster (HEB), into the FCC. Different HEB options are studied: The LHC can be used as pre-accelerator with a reduced beam energy of 3.3 TeV, the super proton synchrotron (SPS) could be upgraded with superconducting magnets to reach an energy of up to 3.3 TeV or a pre-accelerator could be placed in the same tunnel as the FCC. All options have advantages and disadvantages. The baseline is an injection energy of 3.3 TeV provided from the LHC [13, 85]. Due to machine protection reasons a fast and reliable injection system is required in any case. To provide a high reliability of the kicker system, the pulse generator design needs to be fundamentally different from existing former designs. Conventional pulse generator concepts at CERN (Pulse Forming Line (PFL) and Pulse Forming Network (PFN), described in section 2.4) use thyratrons to switch the high voltage and high current pulses which, under certain circumstances, can lead to issues concerning machine safety, reliability and availability [9]. Thyratrons are plasma switching devices which can pre-trigger and may lead to a mis-kick of the beam. Especially for the FCC, a high energy accelerator, a mis-kick of the beam must be avoided to prevent damage of the downstream accelerator equipment due to loss of the beam. To avoid this problem a new pulse generator design based on semiconductor switches instead of thyratrons is required.

First investigations for the FCC injection system showed that a field rise time of 430 ns and a field flat-top length of 2  $\mu$ s, with a maximum ripple of  $\pm 0.5$  %, are required for injection at 3.3 TeV [68, 85]. Transmission

#### Figure 1.1: The CERN accelerator complex [40]

line kicker magnets, similar to the Large Hadron Collider (LHC) injection kicker design, will be used to achieve the fast rise time [29, 31]. The magnet delay time will be in the range of 355 ns hence the pulse generator is required to deliver a pulse rise time of below 75 ns [108]. A summary table of all requirements is given in chapter 4.1. The rather short pulse length allows the consideration of an inductive adder (IA) as a promising option. A major advantage of the IA is its modular design and all control electronics for the solid state switches are referenced to ground potential. The pulse requirements and the low system impedance, chosen for the transmission line kicker magnets [31], create several challenges. An IA as it is required for the FCC injection system has not been built yet.

The IA uses semiconductor based switching devices, instead of thyratrons. Semiconductor based devices, if properly designed and used, are more reliable than plasma switches such as thyratrons. Recent development in the semiconductor market, especially on wide band-gap devices for high power applications, made this technology available for this application. Further improvements in wide band-gap technology can be expected enlarging the design parameter space and facilitating future developments. Besides the switches the IA also brings other advantages compared to traditional pulse generator designs:

For the IA a PFL or PFN is not necessary. The components of the IA are common off-the-shelve components which makes it easy to source and replace them. It is possible to use components from different suppliers in

Figure 1.2: Schematic map of the proposed location of the future circular collider (FCC) [25]

one IA what gives more freedom in component selection and maintenance.

All the mentioned advantages of this new design make the IA not only interesting for kicker systems in future accelerators but also gives the opportunity to replace old generators in existing systems to reduce maintenance costs and profit from further advantages. This dissertation documents the design process, construction and measurements on an IA prototype that has been built for the FCC injection kicker system, reports the results and gives an overview of the challenges and possible improvements.

### 2 Fast pulsed systems

Pulsed systems are used in a wide range of applications in different fields. The focus of this thesis is on applications in experimental physics where pulsed systems are for example used for kicker systems in circular particle accelerators. Other applications where pulsed systems can be found are:

- Radar devices for the generation of radar waves [86]

- Test equipment for high voltage tests conducted on high voltage components [15, 18, 70]

- Electroporation in biotechnology or medicine where cell membranes are made porous to introduce DNA or other material inside the cell or to destroy the cell [17, 47, 78].

- Food processing applications where fruits or vegetables are exposed to high electric fields to improve further treatment [90, 91, 92]

- Research equipment for particle fusion, plasma or laser experiments to provide high power for a short time [18, 66, 104]

- Military applications, e.g. railguns [61, 72, 73]

The references show the big variety of requirements on the pulse systems depending on the application. Pulse lengths of tenth of ns for lasers and up to several ms for railguns, current values from several A up to several kA and voltages up to hundreds of kV are required for the different applications. Since the application of the pulse generator designed and built during this work is a power supply for a kicker magnet the following chapters are focused on pulsed power systems in particle accelerators and specifically kicker systems. Many examples of kicker systems will be related to CERN.

#### 2.1 Injection and extraction systems

For circular particle accelerators the injection and extraction systems are of fundamental importance. Injection systems are injecting the beam from the transfer line from the pre-accelerator to the destination accelerator, onto the circular orbit of the destination accelerator. Extraction systems instead extract the beam from the orbit to the beam transfer line to an experiment, the next accelerator or the beam dump. These beam transitions are fundamental to reach high energy particle beams in a cascaded accelerator complex. Fast extraction and injection are realized with kicker magnets and septum magnets. In the following an injection system is described:

A septum magnet is a magnet with a constant field region and a field free region. The circular orbit of the accelerator is going through the field free region while the constant field region is part of the beam transfer line [8]. Since the two regions of the septum magnet are only separated by a very thin septum it is possible to bring the injected beam very close to the trajectory of the circular orbit. The last kick of the

Figure 2.1: Schematic of an injection system with kicker magnet and septum magnet

injected particle beam that deflects the beam on the circular orbit is generated by a kicker magnet that is placed in the circular beam line of the accelerator. Figure 2.1 shows a schematic of an injection system with septum and kicker magnet.

A fast rising magnetic field of the kicker magnet is necessary to ensure only the injected beam is deflected and a fast fall time is required to not disturb the circulating beam [10]. Therefore the kicker magnet should generate a pulsed magnetic field with a smooth flat-top. To generate the pulsed field a pulse generator is required that serves as power supply for the kicker magnet and fulfills the pulse requirements in terms of voltage, current, rise and fall time, flat-top stability, flat-top length and repetition rate [5, 8, 10]. The different pulse parameters are explained in Figure 2.2.

Figure 2.2: Definition of pulse parameters

Extraction systems work with the same principle as injection systems in reverse order and therefore contain the same components. The injection and extraction process is of high importance for an accelerator complex regarding the beam quality. If the pulse quality and subsequently the field quality of the kicker magnet are not within the tight limits the emittance of the injected beam may grow resulting in a poor beam quality.

#### 2.2 Kicker systems at CERN

The first kicker systems at CERN during the 1960s were moved hydraulically into the beam line. They belonged to the Proton Synchrotron (PS) which started operation on the 24th of November in 1959 [26]. These so called plunging kickers were limited in rise time and aperture. In the 1970s with increasing beam intensity new kicker systems were developed to handle the more challenging requirements on aperture and rise time [45]. The new systems were designed as transmission line type kicker magnets with SF6-gas insulated pulse forming lines. Thyratrons were used as switching elements even though problems such as spontaneous triggering were well known. The relatively low beam energy and some technical improvements to reduce spontaneous triggering made it possible to use this technology in the PS until today [44].

The injection kicker system of the Super Proton Synchrotron (SPS), which was operating from 1976 on [27], contained twelve travelling wave magnets connected in pairs to six pulse generators [69]. The pulse generators were realised as thyratron based pulse forming networks (PFNs) with a maximum operation voltage of 60 kV and a maximum pulse duration of 12  $\mu$ s. For the use of the SPS as injector for the LHC the injection system was modified to achieve faster rise times. The magnet length was reduced and the characteristic impedance increased. To compensate the missing kick strength four additional magnets and two pulse generators had been installed. To fulfill the requirements for proton and ion injection some modifications were carried out resulting in different injection systems depending on the particles [42].

In the LHC hadron injection kicker system (MKI) 4 kicker magnets of the transmission line type design are installed. Each magnet is supplied by one pulse generator realised as a PFN with thyratron switches [22, 41]. With increasing beam energy the effect of a mis-kicked beam and the protection of the machine against damage became more important [21]. Therefore the LHC is equipped with an injection dump (TDI) that absorbs beam losses caused by injection kicker failure [12]. Table 2.1 shows an overview of the injection kicker systems at CERN from the PS to the LHC.

| System               | Unit | PS KFA45      | SPS MKP      | LHC MKI      | FCC          |

|----------------------|------|---------------|--------------|--------------|--------------|

| Magnet design        |      | transm. line  | transm. line | transm. line | transm. line |

| Generator design     |      | PFL           | PFN          | PFN          | IA           |

| Operation mode       |      | short-circuit | terminated   | terminated   | terminated   |

| Magnet impedance     | Ω    | 26.3          | 12.5-16.67   | 5            | 6.25         |

| Generator impedance  | Ω    | 26.3          | 6.25-8.33    | 5            | 6.25         |

| Magnet voltage       | kV   | 40            | 50           | 25           | 15           |

| Magnet current       | kA   | 3.04          | 6-8          | 5            | 2.4          |

| Rise time definition | %    | 5-95          | 0.5-99.5     | 0.5-99.5     | 0.5-99.5     |

| Field rise time      | ns   | 80            | 115-220      | 900          | 75           |

| Field flat-top       | μs   | 2.6           | 0.5-2.1      | 7.86         | 2.3          |

| Flat-top ripple      | %    | $\pm 2$       | $\pm 0.5$    | $\pm 0.5$    | $\pm 0.5$    |

| Fall time            | μs   | 0.104         |              | 3            | 1            |

| Injection energy     | GeV  | 1.4           | 14-26        | 450          | 3300         |

#### Table 2.1: Comparison of injection kicker systems of the CERN accelerator complex

The beam dump system of an accelerator is used to safely dispose of the beam in case of any problem with

the machine or if the beam quality is not good enough for experiments. Even though the beam dump system is a pulsed system, the requirements on the kicker pulse quality are different to injection kicker systems - often flat-top ripple or a decaying sinusoid is required. Nevertheless the kick strength of the dump kicker system needs to follow the beam energy hence the generator of the system is always charged. The extraction kicker systems of a pre-accelerator are often of a similar design as the injection systems of the bigger accelerator since the beam energy is identical. Therefore the extraction kicker systems are not further described here.

#### 2.3 Kicker magnets

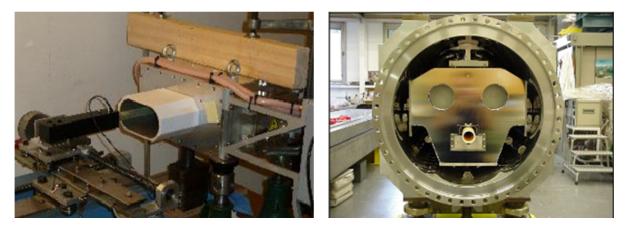

The kicker magnet generates the pulsed magnetic field to deflect single particles, a bunch train or a particle beam of an accelerator. Kicker magnets can be designed to be inside or outside the machine vacuum. Both versions have advantages and disadvantages: in case the magnet is built outside the vacuum chamber it can have an easier design but requires a complex vacuum chamber e.g. made of metallized alumina that requires additional aperture. On the other hand, a kicker magnet inside the vacuum tank needs to be designed out of vacuum compatible materials and requires feedthroughs for all services but the vacuum can also improve the high voltage insulation [6, 10, 67]. Figure 2.3 shows an example for a kicker magnet inside and outside the vacuum chamber. Typical magnet designs are lumped inductance kickers or transmission

Figure 2.3: Left: Example for a kicker magnet outside vacuum. Right: Injection kicker magnet of the LHC inside the vacuum tank as an example for a kicker magnet inside vacuum [6].

line kickers. Lumped inductance kickers are used if fast rise times are not an important aspect. The magnet has a simple design and the generator should be located close to the magnet to reduce inductance [67]. For fast systems the transmission line kicker type is used. To achieve the fast rise time a transmission line kicker is manufactured with a single winding and consists of several cells. The cells contain of c-shaped ferrite cores in between HV plates and ground plates. In this way a broadband coaxial cable is approximated to realize a wide frequency range and therefore fast rise times. The fast rise time magnet design requires a matched impedance in the system to avoid reflections [5, 7, 10].

A different concept of kicker magnet is the stripline kicker magnet where the magnetic and electric field are both used to deflect the beam. It comprises two parallel conductors charged to a positive and negative voltage and a current flowing through the conductors in opposite directions. In the area between the conductors the electric field, caused by the voltage difference and the magnetic field, caused by the current are overlaying and deflect particles in one direction [7].

Any type of kicker magnet can be operated in terminated and short-circuit mode. If a matched resistor is connected to the kicker magnet the system is terminated and after the pulse traveled through the magnet the current and voltage values are constant inside the magnet during the pulse. In case of a short-circuit at the output end of the kicker magnet the pulse is reflected and travels back, doubling the current and cancelling the voltage to zero resulting in a higher kick strength, for a given system impedance, PFN/PFL voltage and magnetic length, but also a longer field rise time. A more detailed description of pulsed systems with matched or short-circuit termination can be found in [54].

#### 2.4 Pulse generators

A pulse generator is needed to supply the kicker magnet with the required power to generate the field. The pulse generator provides a certain current and voltage output to match the requirements for the needed magnet field magnitude, duration, rise time, fall time and ripple. Critical parameters are: current and voltage values, system impedance, pulse rise time, pulse fall time, droop, flat-top stability, pulse-to-pulse stability and repetition rate. Various pulse generator concepts, based on different technologies, can be used to match the requirements of different kicker systems. Some examples for pulse generator designs are explained in the following:

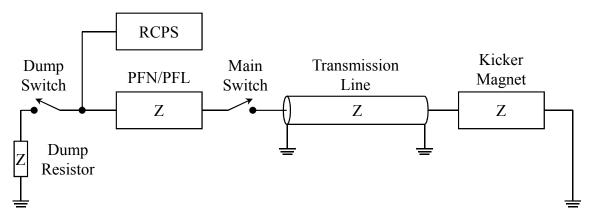

#### 2.4.1 Thyratron switched pulse forming network or line

A common way to generate a pulse is to charge an energy storage network of capacitors and inductors and discharge it via a switch. The network can be realized with lumped elements and is then called a pulse forming network (PFN), or as a coaxial cable then it is called a pulse forming line (PFL). The single-way electrical length of the PFN/PFL should be at least half as long as the required pulse length. After the energy storage is charged with a resonant charging power supply (RCPS) to a voltage V the main switch connects it via a transmission line to a kicker magnet. During that process a negative voltage wave of V/2 is discharging the PFN/PFL and, if the dump switch remains off, it is reflected at the second end. Therefore the total length of the output pulse is twice the electric length of the storage network and the amplitude of the output pulse is half of the charging voltage. A basic component of a PFN/PFL pulse generator is the switching element that discharges the PFN/PFL into the load. In many designs a thyratron is used as switching device. Thyratrons are reliable plasma switching tubes that are able to withstand high overcurrents and can switch very fast. Disadvantages of a thyratron are e.g. high maintenance efforts, possibly required oil cooling and the risk of erratic triggering [9]. An example for a thyratron based PFL is the proton injection kicker system in the PS at CERN (Table 2.1). The simplified schematic of this system is shown in Fig. 2.4.

The described basic version of a pulse generator in a PFN/PFL design can be extended to a system with flexible flat-top length if a second thyratron is connected as a dump switch to the other end of the PFN/PFL. By triggering the dump thyratron before the discharge pulse has reached the end of the storage network, it is discharged from both ends and the pulse length is therefore shortened. If the kicker magnet is terminated the generated pulse is not reflected after travelling through the magnet. A schematic of such a system

Figure 2.4: Schematic drawing of a kicker system with PFN or PFL in short-circuit operation with dump switch and dump resistor [7]

can be found in Fig. 2.4. If the kicker magnet is in short-circuit mode the generated pulse is reflected, cancelling out the voltage and doubling the current in the magnet.

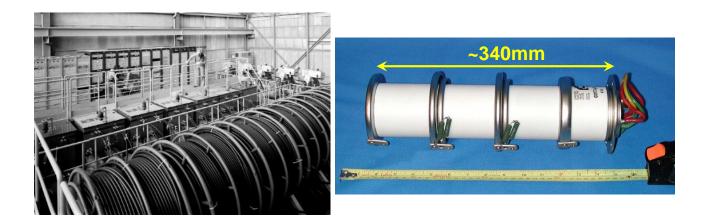

Figure 2.5 shows the reel of PFLs for the KFA45 kicker system, which is used for proton injection in the proton synchrotron (PS) at CERN, and a high voltage thyratron. More detailed information and applications about PFN and PFL based pulse generators can be found in [15, 18, 34].

Figure 2.5: Left: Reels of PFL of the KFA45 pulse generator for the PS proton injection. Right: High voltage thyratron used for pulse generators at CERN [6].

#### 2.4.2 Marx generator

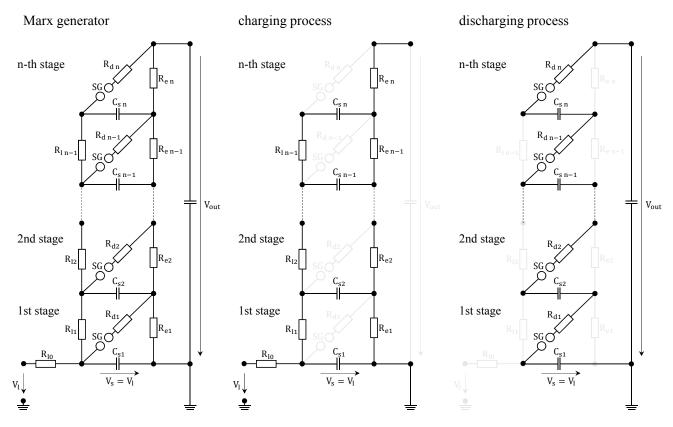

The Marx generator is a standard equipment to generate high pulse voltages and was invented in 1923 by Erwin Marx and is still state of the art for many applications e.g. in high voltage test facilities. Fig. 2.6 shows the schematic of a multi stage Marx generator. The stage capacitors  $C_s$  can be charged in parallel

via the resistors  $R_1$  and  $R_e$  as shown in Fig. 2.6. If the spark gaps (SG) are triggered all capacitors are connected in series through the damping resistors  $R_d$  and the capacitor voltages of all n stages add up at the output voltage of the Marx generator. By changing the resistor values of the schematic the rise and fall times of the Marx generator can be adapted e.g. to generate a standardized lightning pulse wave form on a given load. In high voltage laboratories and test facilities normalized switching impulse voltages and lightning impulse voltages are generated by Marx generators. With well manufactured and adjusted spark gaps a very smooth operation can be obtained [86]. More detailed information, also about solid-state Marx generators, can be found in [14, 15, 18, 34, 52, 70].

Figure 2.6: Schematic of a Marx generator after [15]. Left: full schematic, Center: active components during charging, Right: active components during discharging

#### 2.4.3 Blumlein generator

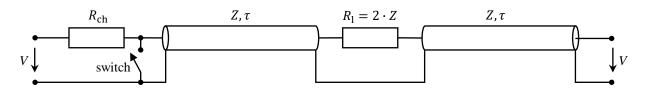

Blumlein generators are often used in physics research experiments to generate electric pulses. The general principle is, as already described for the Marx generator, to charge two networks in parallel and discharge them in series. Two coaxial cables of single-way delay  $\tau$  and with the same pulse impedance Z are connected via a high impedance load  $R_{\rm l} = 2 \cdot Z$ . If both cables are charged to the same voltage V and one end of the cables is switched to short-circuit, the load will see a voltage of V after  $\tau$  that lasts for  $2 \cdot \tau$ . Further information regarding the Blumlein generator can be found in [15, 18].

Figure 2.7: Schematic of a Blumlein generator according to [15]

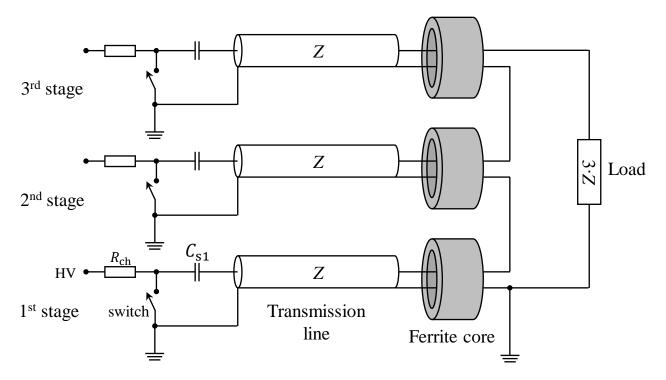

#### 2.4.4 Transmission line adder

The transmission line adder is a voltage adder that consists of several transmission lines connected in such a way that the pulses at the ends are adding up to a high output voltage. A capacitor serves as energy storage and can be discharged via a semiconductor switch into a coaxial cable. The inner conductor on the end of the cable is then connected to the outer conductor on the end of the next stage and so on as shown in Fig. 2.8. By putting correctly dimensioned ferrite cores around the end of the coaxial

Figure 2.8: Schematic of a three stage transmission line adder according to [101]

cable of each stage a magnetic insulation is realised. The length of the cables needs to be long enough to avoid reflections of the pulse during flat-top. Therefore the transmission line adder is only used for short pulses since the cable length should be at least half the physical length of the output pulse flat-top. If the timing of the switches and the travelling time of the pulses is optimised, a very fast pulse rise time in ns range can be accieved [100, 101, 103]. Also the switching performance of the switch needs to be optimised for such short rise times [102]. For applications with several kV and higher load impedance, where very fast rise times and short pulses are required, the transmission line adder is an interesting option [23, 80, 82].

#### 2.4.5 Other pulse generator designs

Marx generator, Blumlein generator and transmission line adder are just a brief overview of possible pulse generator designs. As it can be seen, many designs are taking advantage of the concept of charging capacitors in parallel and discharging them in series. Cascading a circuit with several stages to generate a higher output voltage is another common method and can be found in various applications to generate high AC voltages (cascading transformers [15, 70]) or DC voltages (Greinacher circuit [15, 70]). A different way to generate high voltage pulses is the pulse transformer. The pulse duration is limited by the saturation of the transformer core and a free wheeling current path needs to be added on the primary side of the transformer to avoid a negative backswing. Due to the high inductance of the windings of the transformer the rise time of the pulse is limited but can be optimised [15, 52].

#### 2.4.6 Semiconductor based designs

All mentioned pulse generators are highly relying on the used switch in terms of performance and capabilities. Commonly used switches are spark gaps and thyratrons but also thyristors, which are semiconductor (sc) based closing switches and are only able to switch on. More advanced semiconductor switches such as MOSFETs and IGBTs have the ability to turn on and off. This improvement offers a wider range of options in the pulse generators. Nevertheless, semiconducting switches are not as capable in terms of current and voltage rating as gas switching devices. To reach comparable current and voltage values with semiconducting devices, components need to be switched in series and/or parallel. In case of parallel and series switching the thyratron can be replaced by many sc-switches and the PFN or PFL can still be used as the energy storing component. A problem of series connected sc-switches is the trigger system for the devices that are not grounded on the source pin. As an alternative design the solid state Marx generator can be mentioned. Important is the triggering of the switches in all stages. The trigger system of each stage needs to be galvanically insulated. As switching elements traditionally spark gaps are used but they can also be realised with sc-switches, which make the Marx generator more flexible [84, 89]. The galvanic insulated trigger system of each stage remains a challenge also for the solid state Marx generator. An example for an entirely new pulse generator design which can be realised with sc-switches is the inductive adder, which is described in section 3: the inductive adder does not require galvanically isolated trigger systems.

The used sc-components are usually silicon (Si) based metal oxide semiconductor field effect transistors (MOSFET) or integrated gate bipolar transistors (IGBT). During the last decades the silicon carbide (SiC) technology increased the performance of MOSFETs steadily. Components of several hundred A of pulse current and of up to 1.7 kV rated voltage are available on the market. Compared to Si based MOSFETs and IGBTs the switching time of SiC components is clearly improved and the on-state resistance of the device is reduced, which is important for pulse generators used in kicker systems with low characteristic impedance. This development encourages to think about a pulse generator design based on SiC MOSFETs as switching components.

#### 2.4.7 Limitations of pulse generator designs

Currently used pulse generators in PFN/PFL design were very reliable during the past decades at CERN. During the last years maintenance efforts and the increased difficulties to source various components have become a major concern [112]. The cost of thyratrons recently increased significantly ( $\approx 20000$  CHF): this

is due to the pricing policy of the manufacturer and the very limited number of manufacturers. Additionally, for environmental reasons, the use of sulfur hexafluoride gas (SF6) as part of the insulation medium in the PFL cables in several pulse generators should be reduced or avoided. The replacement of these 40 year old cables has become a big challenge [96].

Besides the maintenance and replacement problems also the erratic triggering is a limitation of a thyratron based pulse generator design. An erratic trigger is the ignition of the thyratron and therefore the generation of a pulse without a trigger signal [9, 60]. Thyratrons are plasma switches and therefore have a certain probability to ignite even if not triggered. The probability for this fault can be reduced by charging the PFN/PFL only a short time before the generator is triggered but can never be eliminated. Consequently accelerators at higher energies need to be equipped with collimation systems that protect the accelerator components downstream of the kicker magnet against the mis-kicked beam or particle showers. In case of higher energy, such as 3.3 TeV, a mis-kick can not be accepted anymore since machine protection efforts and the risk of a quenching superconducting magnet, resulting in downtime for quench recovery, are too high [9, 68].

A new, innovative, reliable and semiconductor based pulse generator would be a big advantage compared to traditional designs. A scalable and modular design that can be readily adapted to various kinds of systems and therefore easily maintained is another strong argument to look into new solutions. During the recent years semiconductor switch capabilities improved significantly in voltage and current capabilities and switching times have been gradually reduced. The mentioned disadvantages of traditional pulse generators and the technological achievements of the last years make it possible to look into a pulse generator design that can offer a highly reliable system, excellent pulse quality and low maintenance. Such a design would strongly improve the operation efforts of an accelerator complex like CERN.

This thesis shows how a semiconductor-based pulse generator, in this cse an inductive adder (IA), can be built for high current (2.4 kA), high voltage (15 kV), fast rise time (75 ns, 0.5 - 99.5 %) and relatively long pulse length (2.3 µs) to fulfill the pulse requirements for the FCC injection. The design and construction of the prototype is publised by the author in [108, 109, 110, 111, 112]. Investigations on the diode current peak after turn-off of an IA with low characteristic impedance were conducted by the author. The results are presented in chapter 4.3.2 and will be published. First investigations on the operation of an IA in a short circuited system are presented in chapter 9.

# **3 Inductive adder principle**