Fakultät Informatik

Institut für Technische Informatik, Professur für VLSI-Entwurfssysteme, Diagnostik und Architektur

# Automatische Dekodersynthese für den retargierbaren Befehlssatzsimulator Jahris

# **Statusvortrag zur Diplomarbeit**

Ronald Rist s0200738@mail.zih.tu-dresden.de

Dresden, 03.07.2013

# Inhalt

# 1 Einleitung

# 2 Grundlagen

- Formale Grundlagen

- Erstellung eines Dekoderbaumes

- Optimierung eines Dekoderbaumes

# 3 Entwurf: Erweiterung der HPADL-Syntax

- Definition von verschiedenen Befehlswortformaten

- Beschreibung von Befehlen

# 4 Ablaufplan

# 5 Ausgewählte Quellen

# 1 Einleitung

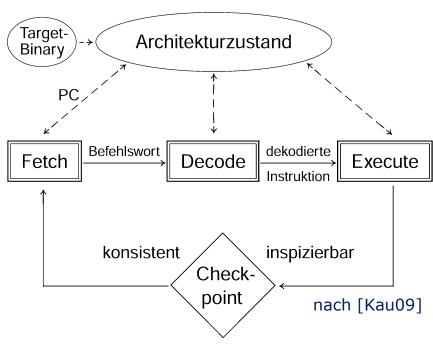

## 1.1 Hintergrund – retargierbarer Befehlssatzsimulator Jahris

von Marco Kaufmann in Java entwickelt, plattformunabhängig

• Simulation verschiedenster Architekturen/Befehlssätze, diese werden

in HPADL beschrieben

Beschränkung auf befehlsgenaue Simulation

- ausgelegt auf hohe Performanz durch Just-in-Time-Compilierung größerer Codeabschnitte

- interpretierende schrittweise

Simulation ebenfalls möglich

## 1.2 Ausgangspunkt

- Vereinbarkeit von Inspizierbarkeit und hoher Simulationsperformanz?

→ in Jahris gewährleistet

- **neue Problemstellung**: Wie kann Entwicklung von Modellen für Jahris vereinfacht werden?

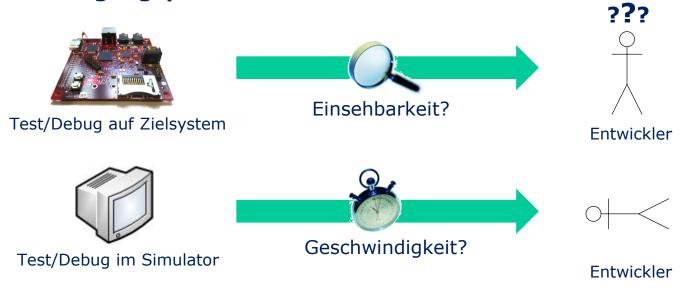

#### 1.3 Motivation

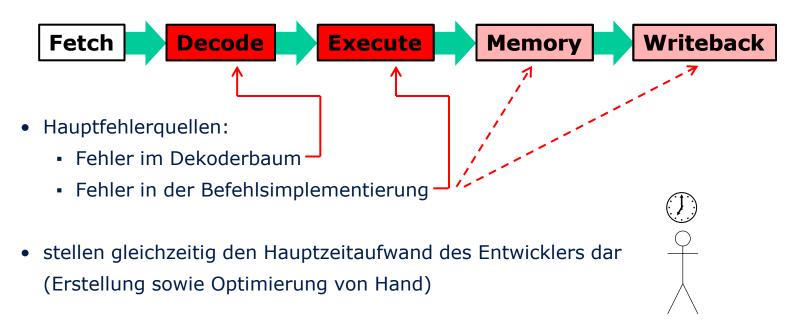

Entwicklung von Architektursimulatoren bzw. Architekturbeschreibungen für retargierbare Architektursimulatoren:

(abstrakte) Abbildung der physischen Pipeline-Stufen

#### 1.3 Motivation (Fortsetzung)

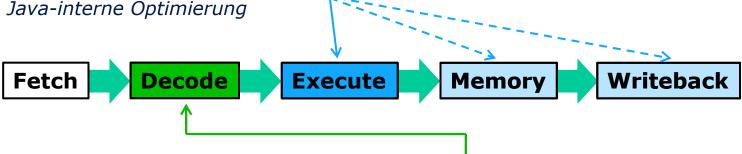

• Jahris: Befehlsimplementierung durch Entwickler, jedoch *maschinelle* Optimierung der Befehle (bzw. deren Mikrooperationen) durch

• Präzisierung der Problemstellung:

Kann Entwickler auch bei Erstellung des Dekoderbaumes entlastet werden?

- maschinelle Erzeugung

- ggf. automatische Optimierung

- → Ausschluss des "Fehlerfaktors Mensch"

# 2 Grundlagen

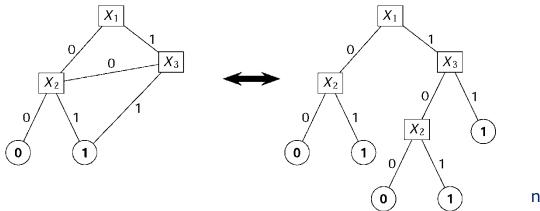

# 2.1 Formale Grundlagen

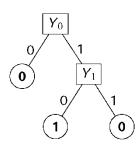

- Abbildung von Befehlsdekodern in sog. Entscheidungsbäumen

- Zuordnung von Befehlsworten zu Operationen schrittweise hierarchisch

#### Baumstruktur

nach [Mor82]

# 2.2 Erstellung eines Dekoderbaumes

- normierte Beschreibung aller verfügbaren Befehle der zu simulierenden Architektur

- Aufgabe:

Entwicklung/Adaptierung eines geeigneten Formats (XML, binär, ...?)

• Repräsentation als "Quelltext" und Repräsentation im Speicher?

# 2.2 Erstellung eines Dekoderbaumes – Was soll abbildbar sein?

| 15 |   |    |    |    | 10  | 9     | 8 |     | 6 | 5     | 3     | 2  | 0     |

|----|---|----|----|----|-----|-------|---|-----|---|-------|-------|----|-------|

| 0  | 0 | 0  | 1  | 1  | 0   | Α     |   | Rm  |   |       | Rn    |    | Rd    |

| 15 |   |    |    |    | 10  | 9     | 8 |     | 6 | 5     | 3     | 2  | 0     |

| 0  | 0 | 0  | 1  | 1  | 1   | Α     | # | imm | 3 |       | Rn    |    | Rd    |

| 15 |   | 13 | 12 | 11 | 10  |       | 8 | 7   |   |       |       |    | 0     |

| 0  | 0 | 1  | С  | )p | F   | Rd/Rn |   |     |   | #imm8 |       |    |       |

| 15 |   | 13 | 12 | 11 | 10  |       |   |     | 6 | 5     | 3     | 2  | 0     |

| 0  | 0 | 0  | С  | )p | #sh |       |   |     |   | Rn    |       | Rd |       |

| 15 |   |    |    |    | 10  | 9     |   |     | 6 | 5     | 3     | 2  | 0     |

| 0  | 1 | 0  | 0  | 0  | 0   |       | С | p   |   | F     | Rm/Rs | F  | Rd/Rn |

| 15 |   |    |    |    | 10  | 9     | 8 | 7   | 6 | 5     | 3     | 2  | 0     |

| 0  | 1 | 0  | 0  | 0  | 1   | О     | р | D   | М |       | Rm    | F  | Rd/Rn |

| 15 |   |    | 12 | 11 | 10  |       | 8 | 7   |   |       |       |    | 0     |

| 1  | 0 | 1  | 0  | R  |     | Rd    |   |     |   |       | #imm8 |    |       |

| 15 |   |    |    |    |     |       | 8 | 7   | 6 |       |       |    | 0     |

| 1  | 0 | 1  | 1  | 0  | 0   | 0     | 0 | Α   |   |       | #imn  | า7 |       |

- (1) ADD SUB Rd, Rn, Rm

- (2) ADD | SUB Rd, Rn, #imm3

- (3) <Op> Rd, Rn, #imm8

- (4) LSL | LSR | ASR Rd, Rn, #sh

- (5) <Op> Rd/Rn,Rm/Rs

- (6) ADD | SUB | MOV Rd/Rn, Rm

- (7) ADD Rd, SP | PC, #imm8

- (8) ADD SUB SP, SP, #imm7

nach [Fur00]

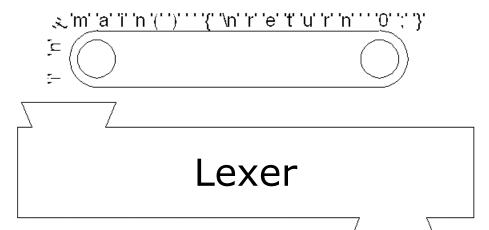

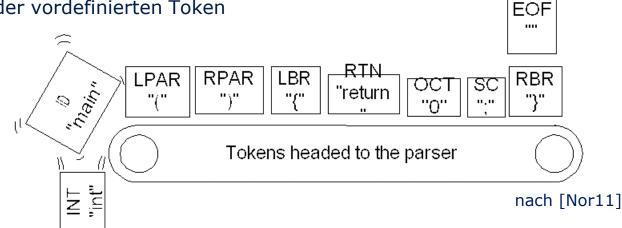

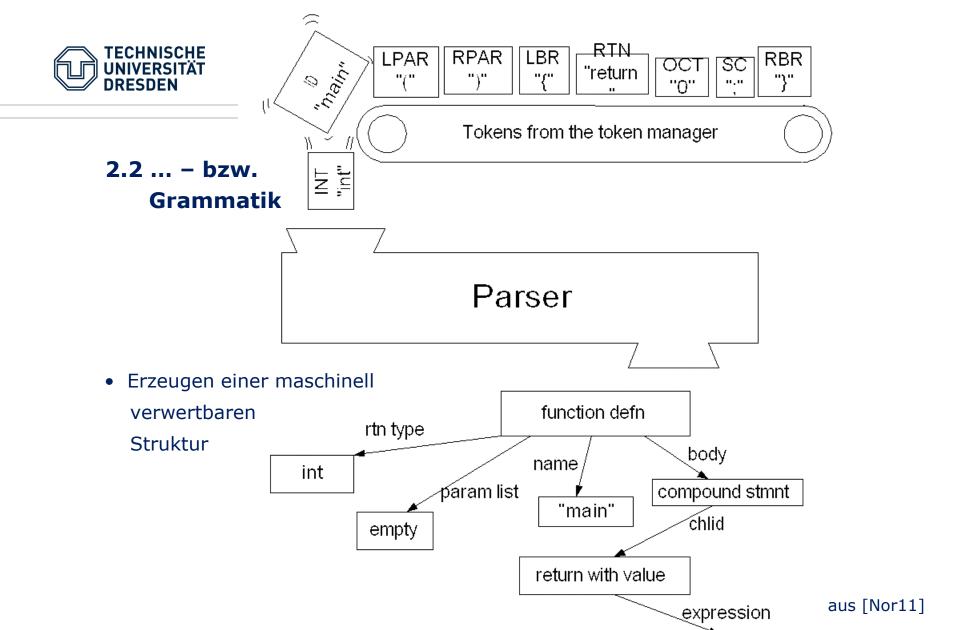

# 2.2 Erstellung eines **Dekoderbaumes -**Verarbeiten einer (neuen) Syntax

- Definition der auszulassenden Zeichen

- Definition der vordefinierten Token

int const

# 2.2 Erstellung eines Dekoderbaumes –Was soll erzeugt werden?

- Beispiel für Hauptdekoderteil (Thumb2)

- bisher manuell zu implementieren

- Vorschlag in [Mur98]:

automatische Kodierung auf

Basis von Auftrittswahrscheinlichkeiten (Shannon-Prinzip)

|                                | Thumb-Hauptdekoder |                    |   |                                                   |                                      |                   |                                     |                           |  |  |

|--------------------------------|--------------------|--------------------|---|---------------------------------------------------|--------------------------------------|-------------------|-------------------------------------|---------------------------|--|--|

| Lookahead-Abwicklung           |                    |                    |   |                                                   |                                      |                   |                                     |                           |  |  |

| Befehlswort (16 Bit) laden     |                    |                    |   |                                                   |                                      |                   |                                     |                           |  |  |

| IT-Block Abwicklung            |                    |                    |   |                                                   |                                      |                   |                                     |                           |  |  |

| Inkrementierung Programmzähler |                    |                    |   |                                                   |                                      |                   |                                     |                           |  |  |

| Befehlswort[3130]              |                    |                    |   |                                                   |                                      |                   |                                     |                           |  |  |

| 0                              |                    | Befehlswort[2927]  | 3 | 3 Befehlswort[2927]                               |                                      |                   |                                     |                           |  |  |

|                                | 0                  | SHimm_th (LSL)     |   | 0 STOREMULTREG_th                                 |                                      |                   |                                     | REG_th                    |  |  |

|                                | 1                  | SHimm_th (LSR)     |   | 1 LOADMULTREG_th 2 CONDBRAN_th 3 CONDBRAN_th      |                                      |                   | ULTR                                | EG_th                     |  |  |

|                                | 2                  | SHimm_th (ASR)     |   |                                                   |                                      |                   | _th                                 |                           |  |  |

|                                | 3                  | ADDSUBr3_th        |   |                                                   |                                      |                   | _th                                 |                           |  |  |

|                                | 4                  | MOVimm_th          |   | 4                                                 | 4 UNCONDBRAN_th                      |                   |                                     | AN_th                     |  |  |

|                                | 5                  |                    |   | 5                                                 | Befehlswort Teil 2 (16 Bit) nachlade |                   |                                     | eil 2 (16 Bit) nachladen  |  |  |

|                                | 6                  | ADDSUB8_th         |   |                                                   |                                      | Befehlswort[2625] |                                     |                           |  |  |

|                                | 7 ADDSUB8_th       |                    |   |                                                   | 0                                    | Befehlswort[2222] |                                     |                           |  |  |

| 1                              |                    | Befehlswort[2927]  |   |                                                   |                                      | 0                 | LO                                  | ADSTOREMULT32_th          |  |  |

|                                | 0                  | Befehlswort[2626]  |   |                                                   |                                      | 1                 | LO                                  | ADSTOREDUAL32_th          |  |  |

|                                |                    | 0 DATAPROC_th      |   |                                                   | 1                                    | DA                | TAPR                                | ROCSHREG32_th             |  |  |

|                                |                    | 1 SPECDATAINSTR_th |   |                                                   | 2                                    | ипі               | gültig                              | (Coprozessor)             |  |  |

|                                | 1                  | LDR_th             |   |                                                   | 3                                    | MC                | $R_M$                               | IRC (Simulated I/O)       |  |  |

|                                | 2                  | LOADSTORE_th       |   | 6 Befehlswort Teil 2 (16 Bit<br>Befehlswort[1515] |                                      |                   |                                     |                           |  |  |

|                                | 3                  |                    |   |                                                   |                                      |                   |                                     |                           |  |  |

|                                | 4                  | LOADSTOREimm_th    |   |                                                   | 0                                    | -                 |                                     | hlswort[2222]             |  |  |

|                                | 5                  | LOADSTOREimm_th    |   |                                                   |                                      | 0                 | _                                   | TAPROCMODIMM_th           |  |  |

|                                | 6                  | LOADSTOREimm_th    |   |                                                   |                                      | 1                 |                                     | TAPROCPLAINIMM_th         |  |  |

|                                | 7                  | LOADSTOREimm_th    |   |                                                   | 1                                    |                   | RANMISC32_th                        |                           |  |  |

| 2                              | _                  | Befehlswort[2927]  |   | 7                                                 | Bei                                  |                   | nlswort Teil 2 (16 Bit) nachladen   |                           |  |  |

|                                | 0                  | LOADSTOREimm2_th   |   |                                                   |                                      |                   | ehlswort[2625]                      |                           |  |  |

|                                | 1                  | LOADSTOREimm2_th   |   |                                                   | 0                                    | $\overline{}$     | Befehlswort[2020]                   |                           |  |  |

|                                |                    | 2 LOADSTOREimm2_th |   |                                                   |                                      | 0                 | $\overline{}$                       | Befehlswort[2424]         |  |  |

|                                | 3                  | LOADSTOREimm2_th   |   |                                                   |                                      |                   | 0                                   | STOREITEM_th              |  |  |

|                                | 4                  | ADR_th             |   |                                                   |                                      | -                 | 1                                   | ungültig (SIMD!LOADSTORE) |  |  |

|                                | 5                  | ADDsp_th           |   |                                                   |                                      | 1                 |                                     | Befehlswort[2221]         |  |  |

|                                | 6<br>7             | Misc16_th          |   |                                                   | _                                    | _                 | 0                                   | LOADHALE th               |  |  |

|                                | _′_                | Misc16_th          |   |                                                   |                                      | _                 | 2                                   | LOADHALF_th LOADWORD_th   |  |  |

|                                |                    |                    |   |                                                   |                                      |                   | 3                                   | ungültig                  |  |  |

|                                |                    |                    |   |                                                   | 1                                    |                   |                                     | 1 , ,                     |  |  |

|                                |                    |                    |   |                                                   | <u> </u>                             | 0                 | Befehlswort[2423]  DATAPROCREG32_th |                           |  |  |

|                                |                    |                    |   |                                                   |                                      | 1                 | DATAPROCREG32_th                    |                           |  |  |

|                                |                    |                    |   |                                                   |                                      | 2                 | MULT32_th                           |                           |  |  |

|                                |                    |                    |   |                                                   |                                      | 3                 | LONGMULT32_th                       |                           |  |  |

|                                |                    |                    |   |                                                   | 2                                    | -                 | unqültig (Coprozessor)              |                           |  |  |

|                                |                    |                    |   |                                                   | 3                                    | <b>├</b> `        | unqültiq (Coprozessor)              |                           |  |  |

|                                |                    |                    | 1 |                                                   |                                      | La ri             | ,9                                  | (                         |  |  |

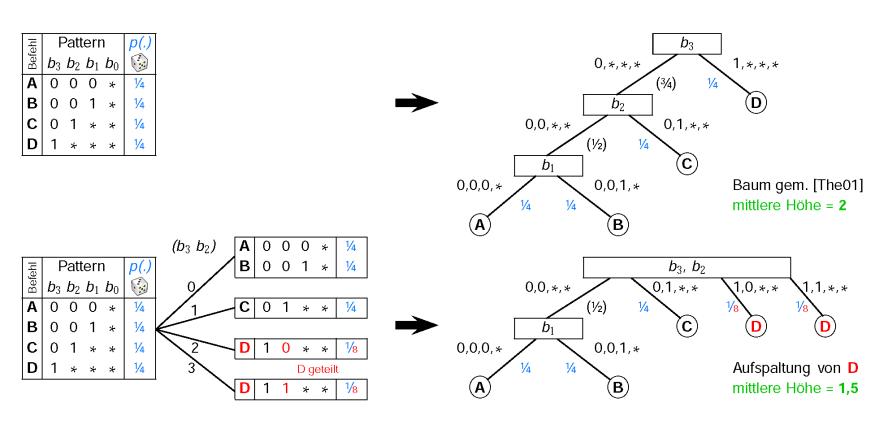

## 2.2 Erstellung eines Dekoderbaumes – Kodierung

nach [Qin+03], modifziert

#### 2.3 Optimierung eines Dekoderbaumes

- Festlegen von Bewertungskriterien für Effizienz

- maximale Baumtiefe (längster Pfad, ungünstigster Überprüfungsaufwand)

- mittlere Baumtiefe (ggf. auch Bewertung von Pfaden mit voneinander abweichenden Auftrittswahrscheinlichkeiten)

- Speichergröße des Baumes

- → ggf. einstellbare Kriterien

- Art und Weise der Optimierung?

- "brute-force": zeitaufwändig, aber: Findung optimalster Lösung garantiert

- → Backtracking zur Reduktion des Aufwands?

- beschleunigte Algorithmen

- → u.U. 90% (oder 99%) des Optimums in einem Bruchteil der Zeit?

# 2.3 Optimierung eines Dekoderbaumes – Lösungsraum

Anzahl möglicher Bäume einer Funktion

$$A_B(k)$$

=  $\prod_{i=0}^{k-1} (k-i)^{2^i}$

$A_B(k+1)$  =  $(k+1) * (A_B(k))^2$

| Anzahl der Variablen k | Anzahl der mögl. Bäume $A_B$ |

|------------------------|------------------------------|

| 1                      | 1                            |

| 2                      | 2                            |

| 3                      | 12                           |

| 4                      | 576                          |

| 5                      | 1.658.880                    |

| 6                      | 16.511.297.126.400           |

| •••                    |                              |

nach [Mor82]

# 2.3 Optimierung eines Dekoderbaumes – Beispiel

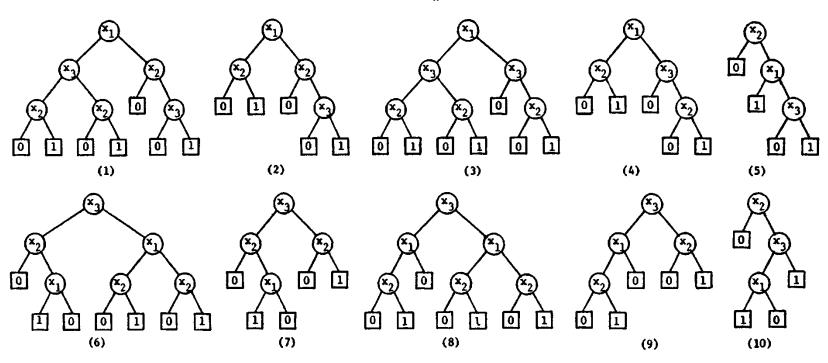

• Beispiel: Bäume der Funktion  $\overline{\mathbf{x}}_1 \& \mathbf{x}_2 \parallel \mathbf{x}_2 \& \mathbf{x}_3$  mit 3 Variablen

aus [Mor82]

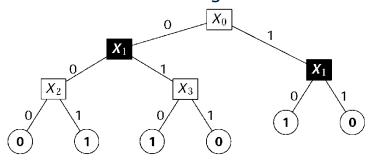

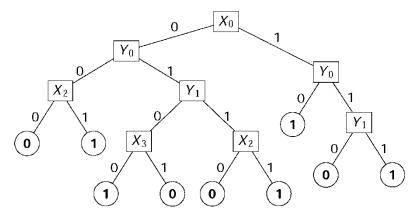

# 2.3 Optimierung eines Dekoderbaumes – Baumkomposition

• Beispiel: Zusammensetzung von Unterbäumen

$$Z = f(X_0, X_1, X_2, X_3)$$

$$X_1 = g(Y_0, Y_1)$$

$$= Y_0 & \overline{Y_1}$$

$$Z = f(X_0, g(Y_0, Y_1), X_2, X_3)$$

=  $f(X_0, Y_0 \& \overline{Y_1}, X_2, X_3)$

=  $h(X_0, X_2, X_3, Y_0, Y_1)$

nach [Mor82]

# 3 Entwurf: Erweiterung der HPADL-Syntax

#### 3.1 Definition von verschiedenen Befehlswortformaten

```

format f3(opc) {

format f1(opc) {

opc: int[6];

opc: int[4];

op1D: int[6];

op1: int[4];

op2: int[4];

op2: int[4];

opD: int[4];

}

format f2(opc,opc2) {

• der Identifikation dienende Opcode-Teile

opc: int[4];

op1D: int[5];

eindeutig vorgeben (vgl. Parameter)

opc2: int[2];

Operanden bereits hart typisieren →

op2: int[3];

vereinfacht z.B. spätere Vorzeichenerweiterung

op3: int[2];

}

```

## 3.2 Beschreibung von Befehlen

• direkte Verwendung von (bisherigem) HPADL-Code in der Befehlsdefinition

```

f2(7,1) { ... }

```

- effektive Definition von geteilten Opcodes (vgl. vorige Folie)

- OFFEN: effizientere Umsetzung des bisherigen Registerzugriffs möglich?

→ parametrisierbarer Aufruf, Umsetzung dennoch zur Dekodierzeit?

```

z.B. ls1(op1); \rightarrow ls1(4); \rightarrow LS1R4;

```

## 3.2 Beschreibung von Befehlen (Fortsetzung)

```

f3(0x1D) { ... }

f3(0b011101) { ... }

```

vorherige Definition der Befehlswortabschnitte →

vereinfachte Lesbarkeit bei "krummen" Längen

```

f3(0x3F) { fetch(16); ... }

```

- Nachladen weiterer Befehlswortbestandteile

- **OFFEN:** Unterteilung in Formate-Block und Befehle-Block *ODER* Intermix mit Hilfe von Keywords (z.B. **format**, **instr**) ?

# 4 Ablaufplan

Vorüberlegungen

#### Nächste Schritte:

- Modifizierung des HPADL-Parsers (parser.jj) zum Einlesen der neuen Syntax

- Implementierung eines *reinen* Dekoderbaum-*Synthese*automaten (Modifizierung des *resolver*)

- Erstellung einer Beschreibung von Thumb im neuen Format (ggf. Modifikationen am neuen Format)

- Synthese dieser Beschreibung, Vergleich mit existierendem Modell, Korrekturen! (kurzes) Benchmark gegen existierendes Modell

#### **MEILENSTEIN!**

- Dokumentation der Implementation

- anschließend: Implementierung von Thumb2, ARM, u.a.

- Erweiterung des Synthesealgorithmus um Optimierung (geringere Relevanz)

- · ausführliche, systematische Benchmarks und deren Dokumentation

# 5 Ausgewählte Quellen

- [Kau09] Kaufmann, M.: Erschließung von Just-in-Time-Compilierungstechniken in der Realisierung eines retargierbaren Architektursimulators, TU Dresden, 2009

- [Mor82] Moret, B. M. E.: Decision Trees and Diagrams, University of New Mexico, ACM, CSUR 1982, S. 593-623, ISSN 0360-0300

- [Qin+03] Qin, W.; Malik, S.: Automated Synthesis of Efficient Binary Decoders for Retargetable Software Toolkits, Princeton University, ACM, DAC 2003, S. 764-769, ISBN 978-1-58113-688-3

- [Nor11] Norvell, Th. S.: The JavaCC FAQ, http://www.engr.mun.ca/~theo/JavaCC-FAQ/javacc-faq-moz.htm